PALTEK、エッジAI向けハードIPのEdgeCortixと提携:FPGAでエッジAI領域の低電力化を

PALTEKは、EdgeCortixと販売代理店契約を結んだ。ザイリンクス製アクセラレーターカードに、EdgeCortixが開発したエッジデバイス用推論プロセッサ向けハードウェアIPを実装し、省スペースや低電力化を必要にするエッジAI用途に提案していく。

自動運転やロボット、スマートシティーなどの用途に提案

PALTEKは2021年2月、EdgeCortixと販売代理店契約を結んだ。ザイリンクス製アクセラレーターカードに、EdgeCortixが開発したエッジデバイス用推論プロセッサ向けハードウェアIPを実装し、省スペースや低電力化を必要にするエッジAI用途に提案していく。

EdgeCortixは、低遅延でエネルギー効率に優れたエッジデバイス向け深層学習推論プロセッサ用ハードウェアIP「Dynamic Neural Accelerator」や、システムソフトウェアなどを開発している。

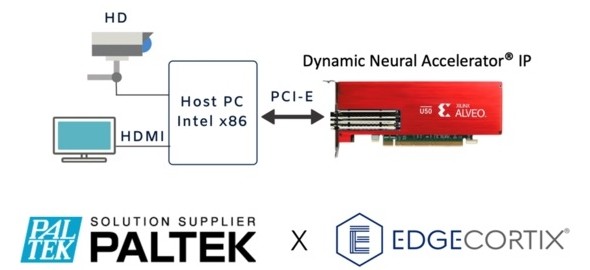

PALTEKは、このDynamic Neural Acceleratorをザイリンクス製FPGAが搭載されたアクセラレーターカード「Alveo U50」に実装。エッジAIソリューションとして自動運転やロボット、スマートシティー、ドローン、インダストリー4.0といった用途に提案していく。

Dynamic Neural Acceleratorの新製品「DNA-F200」は、FPGA上でディープニューラルネットワーク(DNN)推論を高速処理するのに適したIPコアである。HBM(High Bandwidth Memory)に対応するザイリンクス製Alveo U50/U50LV適応型アクセラレーターカード用に設計されているという。

命令セットはINT8ビットバッチサイズ1の推論用に最適化されており、「ResNet」や「YOLO」「SSD」「MobileNet」「FPN」「MonoDepth」など、主要な畳み込みニューラルネットワークに対応している。推論性能は3.7TOPS(300MHz動作時)である。

EdgeCortixは、独自のコンパイラ「MERA」やDNA-F200ビットストリームも提供する。これらを用い、PyTorchやTensorFlow Liteといったフレームワークで開発されたディープニューラルネットワークを、比較的容易にFPGAへ配置することができる。

MERAを用いると、CPUやGPU向けに設計されたネットワークをINT8ビットに量子化し、Alveoに実装されたDNA IP上で最適に実行できるという。MERAには、シミュレーターとインタープリタも組み込まれている。このため、コンパイルした後に、サイクル精度のパフォーマンスシミュレーションをしたり、INT8ビットの量子化がネットワークの精度に与える影響を定量化したりすることが可能である。

関連記事

FPGAに実装可能なエッジAI用ハードIP、45fpsで推論

FPGAに実装可能なエッジAI用ハードIP、45fpsで推論

エッジデバイス用の推論プロセッサ開発を手掛けるEdgecortix(エッジコーテックス)は、「第1回 AI・人工知能 EXPO【秋】」(2020年10月28〜30日、幕張メッセ)で、同社の技術を実装して行うエッジAI(ここでは推論)のデモを展示した。 PALTEK、リアルタイムシミュレーターを発売

PALTEK、リアルタイムシミュレーターを発売

PALTEKは、自動車の開発などで採用が進むモデルベース開発において、コントローラの評価を比較的手軽に行える高速演算リアルタイムシミュレーター「MODEL CUBE」を開発し、販売を始めた。 PALTEKなど3社、車両AI評価キットを共同開発

PALTEKなど3社、車両AI評価キットを共同開発

PALTEKとサイレックス・テクノロジー、ディジタルメディアプロフェッショナル(DMP)は、車両AI評価キット「AISG-GDM-ZIAC3-EV-KIT」を共同開発し、受注を始めた。自動運転機能を搭載する農業機械や建設機械、搬送ロボットなどの開発を支援する。 FPGAで“GPU級”のAIアクセラレーター実現を目指す

FPGAで“GPU級”のAIアクセラレーター実現を目指す

AI(人工知能)ソフトウェアを手掛ける新興企業Mipsologyは2020年6月24日(米国時間)、Xilinxのデータセンター向けアクセラレーターカード「Alveo U50」に、Zebraが統合されたと発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- AIと地政学リスクが招く深刻なメモリ危機

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 26年の半導体市場は64%成長で1.3兆ドルに NAND価格は234%上昇

EdgeCortixのIPコアを実装したザイリンクス製アクセラレーターカード「Alveo U50/U50LV」上で、フルHD解像度の推論を実行するためのシステム例 出典:PALTEK

EdgeCortixのIPコアを実装したザイリンクス製アクセラレーターカード「Alveo U50/U50LV」上で、フルHD解像度の推論を実行するためのシステム例 出典:PALTEK