「ムーアの法則」減速への打開策? ヘテロジニアス設計:PPACの改善を加速(1/2 ページ)

半導体業界では現在、IoT(モノのインターネット)やビッグデータ、AI(人工知能)などによる新しい成長の波が押し寄せている。しかし、半導体イノベーションの必要性がこれまで以上に高まっているにもかかわらず、従来型のムーアの法則の2D(2次元)微細化は、減速の一途にある。

半導体業界では現在、IoT(モノのインターネット)やビッグデータ、AI(人工知能)などによる新しい成長の波が押し寄せている。しかし、半導体イノベーションの必要性がこれまで以上に高まっているにもかかわらず、従来型のムーアの法則の2D(2次元)微細化は、減速の一途にある。

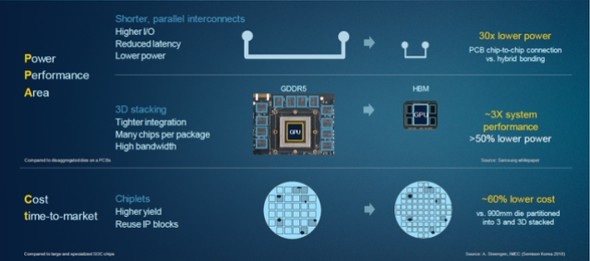

半導体微細化は、世代が進むにつれて、かかる時間もコストも大きくなっていく。このため、半導体メーカーやシステムメーカーが引き続き、電力効率や性能、面積、コスト、市場投入までの期間(筆者が所属するApplied Materialsは、これを「PPACt(Power efficiency, Performance, Area, Cost, and time to market)」と呼ぶ)などを改善し続けていくためには、新しい設計や製造パラダイムが必要だ。

重要性が高まるパッケージング技術

半導体”PPACt”ロードマップは、これまで数十年間にわたり、プレーナー(2D)微細化とモノリシック半導体インテグレーションによって、メトロノームのような正確さで実現されてきた。その間、半導体パッケージングは、業界の中でも価値の低い汎用品と見なされることが多かった。その主な機能は、ダイを保護してPCB(プリント配線板)に接続することにより、半導体チップとモジュール間の電力や信号を伝送することだ。

コンピュータがPCからモバイルデバイスへと進化し、AI時代に突入した今、パッケージングの担う役割は劇的に変化した。現在、高性能パッケージングは、ヘテロジニアス設計やインテグレーションを実現することにより、既存のムーアの法則の2D微細化に伴うPPACtのメリットを継続していく上で、代替手法を提供することが可能になった。大手半導体メーカー/システムメーカー各社が、高性能パッケージングを、競争上の必要不可欠な手段として、ムーアの法則に適用しているところだ。

ヘテロジニアスアプローチを採用すれば、大規模設計を小型のチップレットにディスアグリゲーション(分離)して、シングルパッケージに接続し、PPACtの向上を実現することができる。チップレットを結合させるための方法の1つに、シリコン貫通ビア(TSV)を使用した3D(3次元)スタッキングがある。3DインターコネクトはTSVとよく似ており、既存の配線に比べて大幅に短くなるので、消費電力の削減とI/O密度の向上を実現することが可能だ。

例えば、従来のようにバンプでPCBに接続する場合と比べると、TSVはアーキテクチャやワークロードに応じて、I/O密度を約100倍に高め、1ビット当たりの伝送エネルギーを約15分の1に低減することが可能だ。そのため、電力効率が高い3Dダイスタッキングを実現することができる。また、ロジックとメモリを近接させることで、性能も高められる。

コストを削減するには、2つの方法がある。小型ダイは通常、歩留まりが高く、最先端ノードのウエハーは旧世代プロセス品よりも価格が高い。このため、パフォーマンスクリティカルなダイと他のチップレットとをうまく組み合わせれば、コストを融合して削減することが可能だ。また、実績あるIPチップレットを迅速に組み込むことで、市場投入期間も短縮できる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- Rapidus、IIM-1を「世界初の前/後工程一貫工場に」

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 光電融合チップレットの技術開発を開始 LSTCとimec

- 京セラ、ウシオ電機の半導体レーザー事業を取得へ

- 「技術を束ねて高価値システムに」 デンソーが2030年中計発表