「NVIDIAの時代」の到来 売上高1000億ドル企業の誕生か:湯之上隆のナノフォーカス(73)(2/3 ページ)

NVIDIAのGPUの2つのボトルネック

筆者は、前回のコラム「NVIDIAのGPU不足は今後も続く ボトルネックはHBMとTSMCの中工程か」で、NVIDIAのGPU不足の背景には、2つのボトルネックがあることを詳述した。

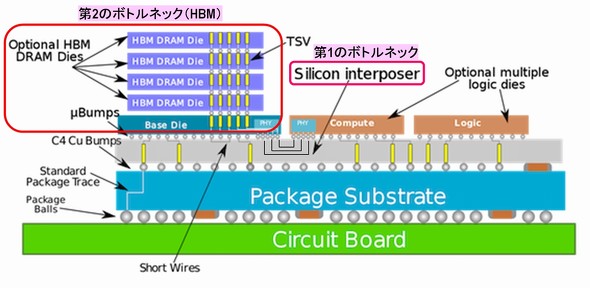

その2つとは、TSMCがNVIDIAのGPU用のCoWoSパッケージを形成するための中工程(の中のシリコンインターポーザ)と広帯域メモリ(HBM)である(図5)。これらがボトルネックとなる理由は、CoWoSが世代を進めるとともに、HBMの搭載数が増える上に、インターポーザの面積が巨大化するからだ。

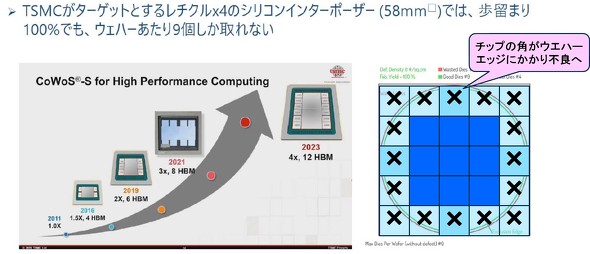

特にインターポーザの巨大化は深刻である。というのは、インターポーザは、12インチシリコンウエハーから角形に切り出したものを使用しているが、インターポーザが大きくなるほど、12インチウエハーからの取得数が減少するからである。

実際に、2023年の第6世代では、インターポーザの面積が3400mm2となり、これで12インチウエハーの面積を割り算すると21個しかインターポーザが取得できない。しかし、現実には、12インチウエハーのエッジかかったインターポーザは全て不良品となるため、面積が3400mm2(58mm□)のインターポーザは最大9個しか取得できない(図6)。

加えて、12インチウエハー上には配線層とTSVを形成しなければならないため、その歩留り(60〜75%)を考慮すると、12インチウエハーから取得できる良品のインターポーザはわずか6個程度になってしまう。

図6 (既出)12インチウエハからインターポーザが何個取得できるか[クリックで拡大] 出所:亀和田忠司、『次世代半導体パッケージング・実装技術動向と市場展望』、サイエンス&テクノロジー主催のセミナー、2024年2月6日

図6 (既出)12インチウエハからインターポーザが何個取得できるか[クリックで拡大] 出所:亀和田忠司、『次世代半導体パッケージング・実装技術動向と市場展望』、サイエンス&テクノロジー主催のセミナー、2024年2月6日インターポーザは今後も巨大化を続ける

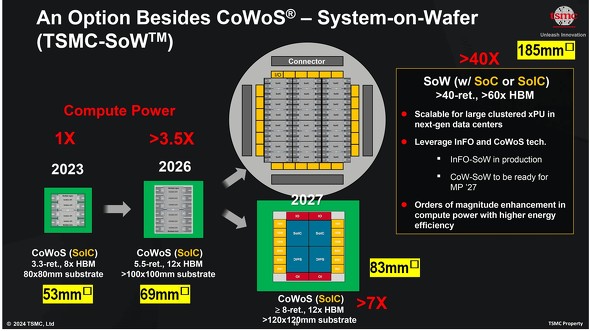

さらに、今後もシリコンインターポーザが巨大化する計画であることが分かった(図7)。それによると、2026年にインターポーザの面積はレチクルサイズの5.5倍以上になると書かれている。レチクルサイズは最大33×26mm=858mm2であるから、その5.5倍は4719mm2(69mm□)になる。58mm□のインターポーザが最大9個であったことから、69mm□のインターポーザは、12インチウエハーから最大5〜6個程度しか取れないのではないか。

図7 インターポーザは今後も巨大化を続ける[クリックで拡大] 出所:Anton Shilov , “TSMC's System-on-Wafer Platform Goes 3D: CoW-SoW Stacks Up the Chips”,ANANDTECH, April 26, 2024, https://www.anandtech.com/show/21372/tsmcs-system-on-wafer-platform-goes-3d-cow-sow

図7 インターポーザは今後も巨大化を続ける[クリックで拡大] 出所:Anton Shilov , “TSMC's System-on-Wafer Platform Goes 3D: CoW-SoW Stacks Up the Chips”,ANANDTECH, April 26, 2024, https://www.anandtech.com/show/21372/tsmcs-system-on-wafer-platform-goes-3d-cow-sowそして、2027年のインターポーザのサイズを見て、筆者は絶望的な気持ちになった。2027年には二通りの計画があり、その一つ(図7の下図)においては、インターポーザ面積はレチクルの8倍以上となっていて、その面積は6864mm2(83mm□)である。恐らく、12インチウエハーから取得できるインターポーザ数は4個以下になるだろう。

さらにもう一つ(図7の上段)では、インターポーザ面積は、何とレチクルの40倍以上となり、その面積は34320mm2(185mm□)である。185mm□のインターポーザは、12インチウエハーから、たった1個しか取得できない。もし、配線層やTSVに不良箇所があれば、取得数はゼロになる!

このように、今後もインターポーザの巨大化が続くとなると、いくらTSMCが毎年、そのCapacityを倍増させたとしても、インターポーザが足りない事態は解消できないだろう。そして、この問題を根本的に解決するには、12インチウエハーからインターポーザを取得するのは止めて、515×510mmの角型有機基板またはガラス基板を使うしかない。しかし、角型基板に配線層とTSVを形成するための製造装置や搬送系を準備するには、年単位の時間がかかる。

以上から、NVIDIAのGPU不足は、今後数年程度では解消できないと思われる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待