強誘電体SRAMやスピンMOS FETが開発、新材料や新機構で微細化限界打ち破る(前編):プロセス技術(1/2 ページ)

Si(シリコン)以外の新たな材料や、新たな動作機構を採用することで、先が見えつつある微細化の限界を引き延ばそう、または乗り越えていこうという研究開発が進められている。

半導体チップの「微細化限界の次」を見据えた研究開発が進んでいる。「現在、製品レベルで30nm〜40nm世代にまで製造プロセスが進んでいる。そろそろ微細化の限界がくるだろう」(東芝研究開発センターのLSI基盤技術ラボラトリーで研究主幹を務める斉藤好昭氏)。

微細化に限界が生じる理由の1つが、電源電圧にある。一般に、微細化を推し進めるには、半導体チップを構成するトランジスタ素子(MOS FET)の電源電圧も引き下げる必要がある。電源電圧を下げることで、微細化に伴って増大する一方の待機時と動作時の消費電力を削減できるからだ。

ところが現実には、電源電圧をこれ以上引き下げるのは、そう簡単ではない。MOS FETのしきい値電圧をこれ以上引き下げるのが難しいことに加えて、微細化に伴ってしきい値電圧のばらつきが増大することが原因だ。「電源電圧は、量産レベルで1.2V、研究開発レベルで1.0Vで止まってしまっている状況だ」(東京大学大学院工学系研究科電気系工学専攻の竹内健氏)という。現在、各企業は製造プロセスの改善を続けているものの、現在のプレーナ型MOS FETの微細化にはいずれ、物理現象に起因した避けられない限界が訪れる。

現在、上記の問題の解決に向けて、Si(シリコン)以外の新たな材料や、新たな動作機構を採用することで、先が見えつつある微細化の限界を引き延ばそう、または乗り越えていこうという研究開発が進められている。

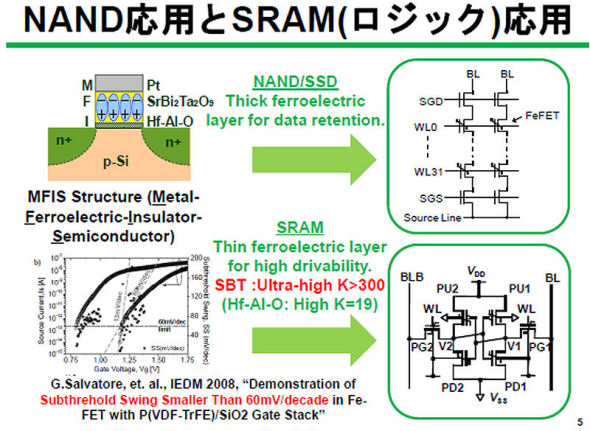

例えば、東京大学の竹内氏の研究グループは、強誘電体材料をゲート電極に使ったSRAM(強誘電体SRAM)を試作し、電源電圧(駆動電圧)を0.5Vにまで引き下げても安定して動作する見通しをつけた(図1)。

また東芝は、電子のスピン方向の差異を動作制御に使ったMOS FET(スピンMOS FET)を開発した。従来と動作機構が大きく異なるスピンMOS FETならば、微細化に伴って電気抵抗やリーク電流が増えてしまうという物理から逃れられるとする。いずれも、2009年12月7〜9日に米国メリーランド州ボルチモアで開催された半導体素子の国際学会「2009 IEEE International Electron Devices Meeting(IEDM 2009)」で発表した*1)、*2)。

ゲート電極に薄い強誘電体膜を利用

東京大学の竹内氏の研究グループでは、新材料を使ってプレーナ型MOS FETの物理限界を引き延ばす試みの第1弾として、強誘電体SRAMの開発に取り組んだ(図2)。

一般に、電源電圧を引き下げるとMOS FETのしきい値電圧Vthのばらつきに対するSRAMの動作安定度が下がってしまう。「High」と出力すべきときに、「Low」と出力する動作誤りの可能性が高まる。SRAMを安定動作させるには、しきい値電圧Vthのばらつきに対する動作マージンを広げる必要があり、これを新材料の採用で実現しようというのが基本的な考え方だ。

図2 強誘電体NAND型フラッシュ・メモリーとの違い 上図が強誘電体を使ったNAND型フラッシュ・メモリーの構造で、下図右が強誘電体SRAMの回路図である。回路構成そのものは、従来のSRAMと何ら変わらない。東京大学の竹内氏の研究グループでは、強誘電体NAND型フラッシュ・メモリーの開発を手掛けていたが、新たにSRAMにも展開した。強誘電体SRAMでは、NAND型フラッシュ・メモリーとは異なり、強誘電体膜を薄くすることで、分極方向を変化させやすくする。

図2 強誘電体NAND型フラッシュ・メモリーとの違い 上図が強誘電体を使ったNAND型フラッシュ・メモリーの構造で、下図右が強誘電体SRAMの回路図である。回路構成そのものは、従来のSRAMと何ら変わらない。東京大学の竹内氏の研究グループでは、強誘電体NAND型フラッシュ・メモリーの開発を手掛けていたが、新たにSRAMにも展開した。強誘電体SRAMでは、NAND型フラッシュ・メモリーとは異なり、強誘電体膜を薄くすることで、分極方向を変化させやすくする。SRAMを構成するMOS FETの数を増やすなど、回路構成を複雑にすることで動作マージンを広げることも可能だが、チップ面積が増大してしまう。強誘電体SRAMでは、SRAMを構成するMOS FETの数や回路構成、面積は、従来と何ら変わらない。

SRAMに注目した理由について同氏は、「システムLSIの回路ブロックのうち、SRAMが最も低電源電圧化が難しい。シンボリックなデバイスとしてSRAMに注目した」と説明した。世界全体を見渡すと、Si材料を使った一般的なロジック回路に、新材料を組み合わせた「エマージング・デバイス」の研究開発が非常に盛り上がりつつあるという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図1 強誘電体を利用したSRAMを開発 しきい値電圧Vthが自動的に変わることが特長だ。

図1 強誘電体を利用したSRAMを開発 しきい値電圧Vthが自動的に変わることが特長だ。