ARMコアとアナログ周辺回路を集積したフラッシュFPGA、アクテル社が投入:プログラマブルロジック FPGA

米Actel(アクテル)社は、英ARM社の32ビット・プロセッサ・コア「Cortex-M3」(以下、M3)をハード・マクロとして集積したFPGA「SmartFusion」を発表した(図1)。同コアを搭載したマイコンはすでに半導体ベンダー各社が製品化しているが、FPGAにハード・マクロとして集積したのは今回が業界初である(図2)。すでに一部の品種については出荷に応じられるとしており、実際に早期採用企業に向けて6カ月前から提供を始めているという。

Actel社は従来から、プログラム領域の基本素子にフラッシュ・メモリー・セルを使う不揮発性FPGA「ProASIC3」や、ProASIC3にアナログ周辺を混載したFPGA「Fusion」を供給していた。さらに2007年からはこれらのFPGAに向けて、プログラム領域に実装するソフト・マクロ形式のARMコア「Cortex-M1」も提供していた。

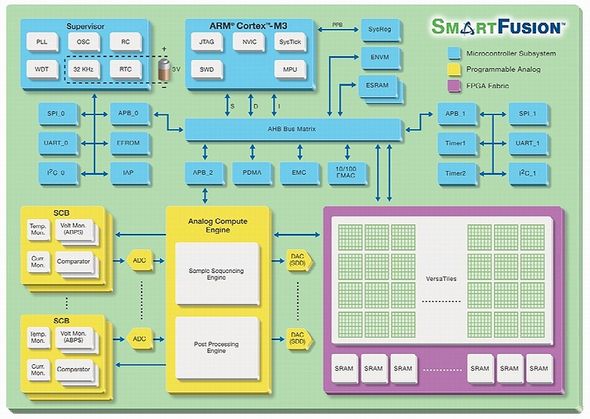

図2 SmartFusionの機能ブロック図

図2 SmartFusionの機能ブロック図FPGAのプログラム領域(ファブリック)と、Cortex-M3コアを中核とするMSS(Microcontroller Sub System)、アナログ周辺回路を1チップにまとめた。出典:米Actel社

今回のSmartFusionは、従来品のFusionを基に、新たにM3コアをハード・マクロ形式で集積するとともにアナログ周辺回路の特性や機能を高めた上位品種である。「これまで汎用マイコンに単体アナログICや小規模FPGA、CPLDなどを組み合わせて構成していた機能を、1個のSmartFusionで実現できる」(同社でマーケティング&エンジニアリング担当の上級副社長を務めるFares Mubarak氏)と主張する(図3)。具体的には、モーター制御や電力管理、マイコン・システム管理などの機能の実装に使えるという。

プログラム領域の集積規模が異なる3品種を用意した(図4)。具体的には、システム・ゲート数が6万個(論理セル「VersaTile」の搭載数は1536個)の「A2F060」と、20万個(同4608個)の「A2F200」、50万個(同1万1520個)の「A2F500」である。いずれの品種もプログラム領域の動作周波数は350MHz。A2F200はすでに出荷を開始しており、A2F500は2010年第2四半期、A2F060は同第4四半期に出荷を始める予定だ。

プロセッサの周辺機能もサブシステムとして搭載

プロセッサ・コアをハード・マクロとして集積したことのユーザー・メリットについては、ソフト・マクロとしてプログラム領域に実装する場合に比べてコアの動作周波数を高くできる点や、プログラム領域を消費しないため集積規模が比較的小さいFPGAを採用できる可能性があり、コストを抑えられる点などを挙げている。

例えば、従来品のProASIC3と今回のSmartFusionはともに0.13μm世代のプロセス技術で製造するが、ProASIC3にソフト・マクロ形式で実装する前述のM1コアの動作周波数が最大72MHzだったのに対し、SmartFusionのM3コアは100MHzで動作する。また、ProASIC3にM1コアを実装する際には、最小4300個の論理セル(VersaTile)を消費していた。

さらにSmartFusionでは、M3コアの周辺機能も搭載している。具体的には、AHB(Advanced High-Performance Bus)のバス・マトリクスと、同バスを介してM3コアにつながるフラッシュ・メモリーやSRAM、10/100イーサーネットMAC(Media Access Control)、DMAなどのほか、UART/SPI/I2Cといったインターフェース、さらにウオッチドッグ・タイマーやリアルタイム・クロックなどで構成したスーパーバイザ・ブロックなどである。SRAMとフラッシュ・メモリーの容量はFPGAの品種によって異なり、SRAMが最大64Kバイト。フラッシュ・メモリーについては最大512Kバイトを確保しており、プログラム・コードやOSをFPGAチップ内に格納しておくことが可能だ。

Actel社はM3コアとこれらの周辺機能をまとめて「MSS(Microcontroller Sub System)」と呼ぶ。FPGAのプログラム領域とMSSは、前述のAHBのバス・マトリクスを介してFPGAのチップ内部で接続する仕組みである。一般的なFPGAとマイコンを採用してプリント基板上の配線で両者をつなぐ場合とは異なり、SmartFusionではインターフェースがチップ外部に露出しないためセキュリティが高く設計資産を保護しやすいとしている。

アナログ周辺回路の特性と機能が向上

このほかSmartFusionでは、先に述べた通り、アナログ周辺回路の特性や機能も高めた。電圧/電流/温度モニター回路と高速コンパレータ回路を統合した「シグナル・コンディショニング・ブロック(SCB)」と、A-D変換器、D-A変換器をそれぞれ複数チャネルずつ集積する。これらをまとめて「アナログ・フロントエンド(AFE)」と呼ぶ。

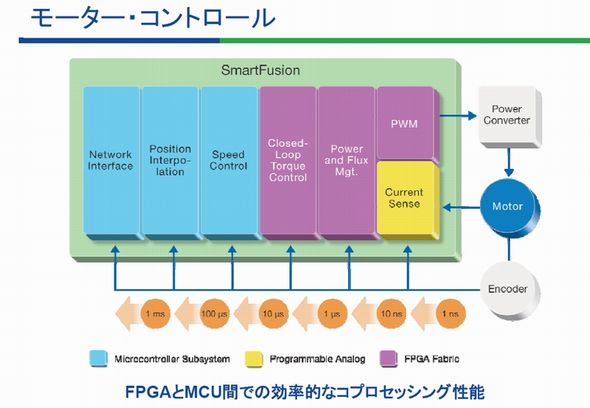

SCBは最大5チャネルを搭載。各SCBには、高速コンパレータ回路も統合した。MSSのソフトウエア処理でもFPGAプログラム領域のハードウエア処理でも対応できない、応答時間が数十ns以下と短くループ処理速度が高いモーター制御などのアプリケーションに使える(図5)。A-D変換器は分解能が8〜12ビットで最大600kサンプル/秒動作のSAR(逐次比較)型、D-A変換器は12ビットのΔΣ型をそれぞれ最大3チャネルずつ内蔵した。

図5 ハード処理とソフト処理の分割で性能を最適化

図5 ハード処理とソフト処理の分割で性能を最適化モーター制御アプリケーションの実装イメージである。比較的長い応答時間が許容される処理はM3コアによるソフトウエア処理、短い応答時間が求められる処理はFPGAのプログラム領域でハードウエア処理、極めて短い応答時間を達成しなければならない処理はアナログ周辺回路の高速コンパレータを使う。出典:米Actel社

さらに、AFEの各構成要素の初期化や制御を担う小型プロセッサ「アナログ・コンピュート・エンジン(ACE)」も搭載した。M3コアの処理負荷を軽減(オフロード)する役割を担い、SmartFusionに実装するシステム全体のスループットを高められるほか、消費電力も低減できるという。従来品のFusionは、電圧/電流/温度モニター回路と外付けパワーMOS FET用ゲート・ドライバからなる「Analog Quad」と呼ぶアナログ・ブロックを最大10チャネル集積していたが、高速コンパレータは用意していなかった。また内蔵するA-D変換器は600kサンプル/秒の12ビット品が1チャネルだけで、ACEも搭載していなかった。

設計環境も拡充

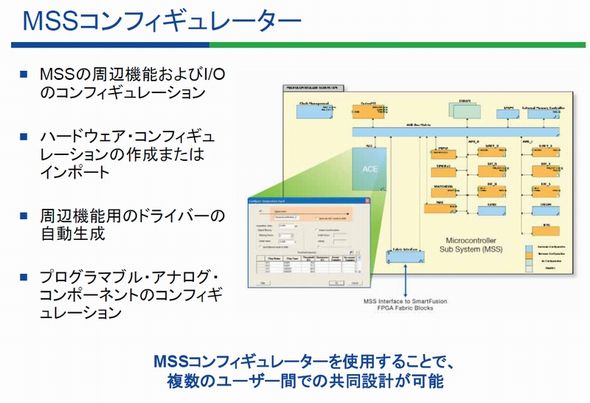

SmartFusionでは、M3コアの集積やアナログ周辺回路の改良に併せて、FPGA開発環境も拡充した。具体的には、「MSS Configurator」と呼ぶグラフィカル・ツールを新たに用意した。M3コアを中核とするMSSの周辺機能と入出力ポートの構成(コンフィギュレーション)や、AFEとACEのコンフィギュレーションをツールの画面上で対話的に設定できるほか、周辺機能用のドライバ・ソフトウエアを自動的に生成したりできる(図6)。

FPGAのプログラム領域に実装するユーザー論理の設計環境としては、従来通り同社の「Libero」を供給する。M3コア向けの組み込みソフトウエア開発環境(IDE)については、同社の「SoftConsole」のほか、スウェーデンIAR Systems社やARM社の子会社である米Keli社の製品を利用可能だ。

なおCortex-M3コアを集積し、デジタルとアナログの周辺機能をユーザーが手元でカスタマイズできるチップとしては、SmartFusionのほかにも米Cypress Semiconductor社が2009年9月に発表した「PSoC 5」がある。PSoC 5はPLDベースのプログラマブルな汎用論理ブロックも搭載しており、SmartFusionと同様に、汎用マイコンに単体アナログICや小規模FPGA、CPLDなどを組み合わせて構成していた機能を1チップで置き換えることを狙う。

これについてActel社は、「PSoC 5は優れたマイコンだ。例えば、アナログの周辺機能については、SmartFusionよりも充実している」(同社のMubarak氏)としながらも、「SmartFusionの方がCortex-M3の動作周波数が高い。またPSoCはプログラマブル論理ブロックをごくわずかしか搭載していないので、ユーザー任意の大規模な論理回路を実装することは不可能だ。SmartFusionであれば、そうした制約はない。ユーザーが既存のFPGAで開発済みの論理回路を搭載できる」(同氏)と述べ、性能や設計柔軟性を重視する用途では優位性があると主張した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

図1 米Actel社が発売したFPGA「SmartFusion」

図1 米Actel社が発売したFPGA「SmartFusion」 図3 Fares Mubarak氏

図3 Fares Mubarak氏 図4 SmartFusionの品種構成

図4 SmartFusionの品種構成 図6 周辺機能のコンフィギュレーション用ツール

図6 周辺機能のコンフィギュレーション用ツール