SOI基板を不要に、米Innovative Silicon社がキャパシタ・レスDRAM技術を改良:メモリ/ストレージ技術 DRAM

データの保持にキャパシタを使用しないDRAM技術「Z-RAM」を開発している米Innovative Silicon社は、一般的なSi(シリコン)基板上にZ-RAM技術を応用したDRAMセルを作った試作品の開発に成功したと発表した。これまで同社のZ-RAM技術はSOI(Silicon On Insulator)基板が必要だったが、3次元構造のトランジスタを利用することで、一般的なSi基板を利用できるようになったという。

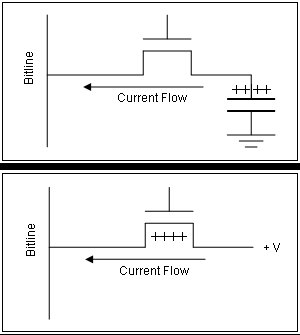

既存のDRAMでは、1ビットのデータを保持するセルを、キャパシタとトランジスタ(MOS FET)の組み合わせで構成している(図1)。しかし、半導体の微細化が進むにつれて、キャパシタの体積が小さくなり、蓄積できる電荷量が少なくなってきている。微細化をさらに進めると、DRAMセルとして機能するために十分な電荷も蓄積できなくなる可能性がある。

そこで、Innovative Silicon社などの企業がキャパシタを省き、MOS FETのゲートに電荷を蓄積する「キャパシタ・レスDRAM(フローティング・ボディDRAMとも呼ぶ)」の研究を続けている。キャパシタ・レスDRAMはキャパシタを必要とせず、MOS FETが蓄積する微小な電荷で動作するため、チップ当たりの記録密度を上げやすく、さらなる微細化にも対応できる可能性がある。

図1 一般的なDRAMとZ-RAMのメモリー・セルの違い

図1 一般的なDRAMとZ-RAMのメモリー・セルの違い一般的なDRAM(上)はドレイン電極にキャパシタを接続する。Z-RAM(下)ではキャパシタは使わない。データを書き込むには、ゲート電極にしきい電圧以上の電圧を印加する。次にドレイン電極に正電圧を加えることで、ソース電極からドレイン電極に向かう電子のエネルギにより、フローティング・ボディに正孔がたまる。ボディに蓄積された電荷の有無によってセル電流が変化するため、データの読み出しが可能になる。出典:米Innovative Silicon社

今回、Innovative Silicon社の依頼で試作を請け負ったのは、韓国Hynix Semiconductor社。54nm製造技術を適用した今回の試作品は、1V以下の電圧で動作するという。この結果を受けて、Innovative Silicon社は、「Z-RAM技術を応用したDRAMは、低コストで製造でき、動作電圧を低くすることも可能だ。これで、Z-RAM技術が既存のDRAMに代わる技術として有力であることを実証できた」と主張する。

Innovative Silicon社は2002年設立の企業。現時点では株式は公開していない。同社は今回の発表では、技術の詳細を明らかにはしないという。これ以上の詳細な情報は、2010年6月15日〜18日に米ハワイ州ホノルルで開催予定の半導体関連の国際学会「2010 Symposia on VLSI Technology and Circuits(VLSI 2010)」で明らかにするという。この学会で、Innovative Silicon社は、Hynix Semiconductor社と共同執筆した論文を発表する予定だ。「この論文で、メモリー・セルの動作電圧などの詳細を明らかにする」としている。

Si基板上にキャパシタ・レスDRAMを集積すれば、高価なSOI基板が不要になる。Innovative Silicon社は、「40nm以降の製造技術では、Z-RAM技術を利用したDRAMは既存のDRAMよりも低いコストで製造できるようになるだろう。もちろん、DDR(Double Data Rate)技術にも対応可能だ」と主張する。

Innovative Silicon社でプレジデント兼CEOを務めるMark-Eric Jones氏は、「Z-RAM技術を大幅に改善できたことに興奮している。メモリー・メーカー各社は、Si基板を使って、既存のあらゆるDRAM技術よりも低いコストでDRAMの製造を可能にする技術を求めている。今回の改善で、この要望に応えることができるだろう」と述べた。さらに、「既存のDRAM技術は40年もの間、低コストでランダム・アクセス・メモリー(RAM)を製造できる技術として使われている。しかし、メモリー業界は、キャパシタを使わない技術に移行しようとしている」と付け加えた。

Innovative Silicon社でチェアマン兼Chief Technology Officerを務めるPierre Fazan氏は、「今回の改良で、Z-RAM技術は既存のDRAMに取って代わるのに必要な特長をすべて備えたことになる。Si基板を使った試作品では、1V以下の動作電圧でも、データを静的に保持できる時間が短くなることはないと実証できた。また、DRAMとして実際に動作させたときのデータ保持時間を1000倍以上に高められることも確認した。Z-RAM技術は、他社が開発、発表しているキャパシタ・レスDRAM技術やサイリスタ・メモリーと比べて、動作電圧を50%〜70%低くできる。Z-RAM技術は、国際半導体技術ロードマップ(ITRS:International Technology Roadmap for Semiconductor)の予測によるメモリー・ロードマップに追随できる唯一のキャパシタ・レスDRAM技術だ」と今回の改良の意義の大きさを強調した。

Hynix Semiconductor社でDRAM研究開発部門のバイス・プレジデントを務めるSungjoo Hong氏は、「54nm製造技術による試作品は、Z-RAM技術が、ほかのキャパシタ・レスDRAM技術が抱える課題を克服したことを実証した。この結果は、今後数世代先の間にZ-RAM技術が既存のDRAM技術に取って代わる可能性があることを示している」と述べた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- AI/HPCシステムの死命を制する消費電力・放熱設計(後編)