アルテラ社が28nm FPGAの製品概要を発表、ES出荷を2011年Q1に開始:プログラマブルロジック FPGA

FPGAの大手ベンダーである米Altera(アルテラ)社は、28nm世代の製造技術を適用した次世代のハイエンドFPGAの製品概要を発表した。製品ファミリ名は「Stratix V(ストラティクス・ファイブ)」。40nm世代で製造する現行品「Stratix IV(フォー)」の後継品となる。2011年第1四半期(1〜3月)にエンジニアリング・サンプル品の出荷を始める計画だ。それに先立って2010年第2四半期(4月〜6月)中にFPGA開発ツール「Quartus II」をStratix Vに対応させる予定である。

同社はすでに2010年2月初旬に、28nm世代のFPGAに適用する新技術については公表していた。ただし、製品ファミリ名や具体的な品種構成、出荷時期などについては「2010年の後半に改めて発表する」(同社のプロダクト&コーポレート・マーケティング担当バイスプレジデントを務めるVince Hu氏(図1))として、その時点では明らかにしていなかった。今回はこれらを2月時点の予告よりも前倒しして発表した格好である。

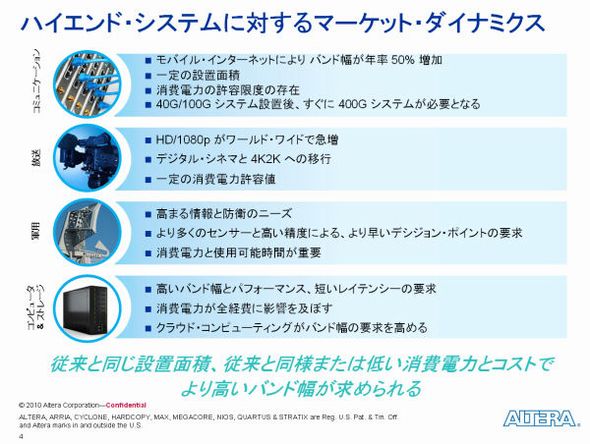

同社は、最先端の製造技術を採用したFPGAを継続的に市場投入することで、通信インフラや産業、コンピュータ/ストレージといった対象分野で、ASSP(Application Specific Standard Product)やASIC(Application Specific Integrated Circuit)からFPGAへの置き換えを促していきたい考えだ(図2)。「現在、ASICでは130nm世代の製造技術が主流であるのに対して、FPGAでは3世代も微細化が進んだ40nm世代が主流である。40nm世代において、FPGAのコストやパフォーマンスがASICやASSPを追い越す転換点に到達したと考えている。さらに微細化を進めた製品ファミリを市場に投入することで、カスタム・ロジック市場におけるFPGAの割合を高めていきたい」(日本アルテラの代表取締役社長を務める日隈寛和氏)とする。

図2 28nm世代のFPGAが狙う主な用途

図2 28nm世代のFPGAが狙う主な用途通信インフラ(コミュニケーション)や放送、産業、軍事、コンピュータ/ストレージといった分野では、実装面積や消費電力の削減、バンド幅の拡大に対する要求が強い。28nm世代のFPGAを製品化することで、これらの市場要求に応えられるとする。出典:日本アルテラ

4つのサブファミリを用意

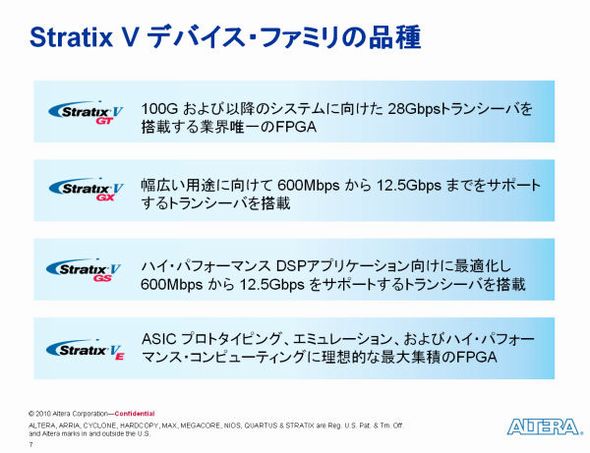

Stratix Vは、最大110万ロジック・エレメント(LE)相当のユーザー・ロジックを集積する。動作周波数は最大350MHz。53Mビットのメモリー(RAM)を搭載するほか、18×18ビット乗算器で最大3680個に相当するDSPブロックや、最大28Gビット/秒で動作する高速シリアル・トランシーバも内蔵する。4つのサブファミリを用意しており、それぞれ異なる応用分野に向けて特性を最適化した(図3)。

1つ目は28Gビット/秒動作の高速シリアル・トランシーバを集積した「Stratix V GT」で、100Gビット/秒から数百Gビット/秒の通信機器に向ける。2つ目は600Mビット/秒〜12.5Gビット/秒動作の高速シリアル・トランシーバを搭載した「Stratix V GX」で、幅広い用途に使える中級品種と位置付ける。3つ目は高性能のデジタル信号処理アプリケーションに向けて最適化した「Stratix V GS」で、この品種も最大12.5Gビット/秒動作の高速シリアル・トランシーバを内蔵する。4つ目は、高速シリアル・トランシーバを搭載せずに、ユーザー・ロジックの集積規模を最大化した「Stratix V E」で、ASICのプロトタイピングやエミュレーションのほか、スーパー・コンピュータ(HPC)などに向くという。

なお、これら4つのサブファミリそれぞれの詳細な品種構成や各品種の仕様については、「各サブファミリの製品発表を今後改めて行い、その際に明らかにする」(同氏)としている。

ALMやDSPも改良

このほか今回は、2月初旬の発表では説明していなかったStratix Vの改善点についても説明した。

まず、Stratixシリーズの基本ロジック・ブロックである「アダプティブ・ロジック・モジュール(AML)」のアーキテクチャを改良し、ロジック回路の実装効率と性能を高めた。具体的には、AMLの内部に出力レジスタを2個追加した。これにより、ユーザー・ロジックの集積規模が最大の品種ではFPGA全体で出力レジスタが80万個も増えるという。特に、パイプライン処理を多用する回路やレジスタを数多く消費する回路に有効だとしている。

さらに、ハード・マクロ(ハードIP)として集積するDSPブロックを改良し、デジタル信号処理性能を大幅に高めた。具体的には、前述の通り、18×18ビット乗算器で最大3680個に相当するDSPブロックを集積する。Stratix IVでは最大1288個相当にとどまっていた。加えて、乗算器の精度をユーザーが用途に応じて手元で変えられるようにした。具体的には、18×18ビットのほか、9×9ビットと18×36ビット、27×27ビット、36×35ビット、54×54ビットをユーザーがアプリケーションに合わせて任意に選択できる。しかも、浮動小数点演算(単精度および倍精度に対応)も標準でサポートした。1個のFPGAで最大1840GMACSの積和演算もしくは最大1000GFLOPSの浮動小数点演算を実行可能だという。

28G高速トランシーバはチャネル当たり200mW

また今回は、2月初旬に明らかにした28nm世代品の新技術についても追加の情報があった。

28Gビット/秒動作の高速シリアル・トランシーバについては、チャネル当たりの消費電力が200mWで、1Gビット/秒換算で7mWに相当すると説明した。CEI-28Gに準拠するように設計したという。集積するチャネル数は明らかにしていないが、「1個のFPGAで最大1.6Tビット/秒のシリアル伝送能力を実現できる」(同氏)としている。

ユーザー任意の論理回路をハード・マクロ化して集積する技術「Embedded HardCopy Blocks」については、3つの段階に分けて順番に利用できるようにすると説明した。当初はアルテラ社が自社のFPGAの品種を拡充する際に使う。次の段階では、同社のパートナ企業が独自のIPコアをFPGAに埋め込んで機器メーカーに提供できるようにする。最終的には、機器メーカー自体が任意の論理回路をIPコアとして集積できるようにする。ただし、パートナ企業や機器メーカーがこの技術を利用できるようになる時期は、現時点ではいずれも未定だという。さらに、従来世代と同様にStratix Vでも、FPGAの設計データを基にストラクチャードASICを製造して供給するサービス「HardCopy」を提供する。「HardCopy V」と呼ぶ。ただし詳細については後日発表する予定だとした。

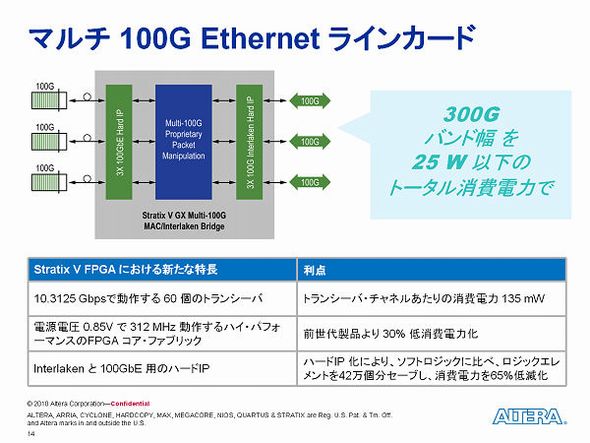

このほか今回はStratix Vで想定する応用例もいくつか示した。例えば、300Gビット/秒対応イーサネットのライン・カードでは、Stratix Vが内蔵する通信処理用ハードIPを活用する(図4)。具体的には100Gビット/秒対応イーサネット用ハードIPと、チップ間のインターコネクト・プロトコルであるInterlaken用ハードIPを各3個ずつ使う。Interlaken用ハードIPは、イーサネット用ハードIPと同様に100Gビット/秒に対応している。これらに60チャネルの高速シリアル・トランシーバを組み合わせ、それぞれ10.3125Gビット/秒で動作させる。後はユーザー・ロジック領域にイーサネットとInterlakenのプロトコルを橋渡しするパケット処理回路を実装すればよい。

10.3125Gビット/秒動作時の高速シリアル・トランシーバの消費電力はチャネル当たり135mW。ユーザー・ロジック領域は312MHzで動作し、電源電圧が0.85Vと低いので、現行のハイエンドFPGAよりも消費電力を30%低減できるという。また、前述の通信処理用ハードIPはロジック・エレメント換算で42万個に相当する回路規模があり、同等の回路をユーザー・ロジック領域にソフト・マクロとして実装する場合に比べて消費電力を65%低く抑えられるとしている。これらの結果、300Gビット/秒の帯域幅を合計25W以下の消費電力で実現できるという。

<訂正事項>記事掲載当初、「2010年第4四半期(10〜12月)にFPGA開発ツール「Quartus II」をStratix Vに対応させる予定」としていましたが、正しくは、「2010年第2四半期(4月〜6月)中にFPGA開発ツール「Quartus II」をStratix Vに対応させる予定」です。本記事は、すでに修正済みです。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

図1 28nm世代のFPGAの特長を説明するVince Hu氏

図1 28nm世代のFPGAの特長を説明するVince Hu氏 図3 Stratix Vファミリの構成

図3 Stratix Vファミリの構成 図4 Stratix Vで想定する応用例

図4 Stratix Vで想定する応用例