用途によって変わるMOSFETの選択基準:パワー半導体

MOSFETは成熟した電子デバイスなので、品種の選定は一見簡単なように思える。確かにユーザーは、MOSFETのデータシートに記載されている性能指標(Figure of Merit:FOM)についてはよく理解している。ただし実際の品種選びでは、エンジニアが専門知識を駆使して、どのような機器に適用するかに合わせてMOSFETの特性を精査する必要がある。

MOSFETは成熟した電子デバイスなので、品種の選定は一見簡単なように思える。確かにユーザーは、MOSFETのデータシートに記載されている性能指標(Figure of Merit:FOM)についてはよく理解している。ただし実際の品種選びでは、エンジニアが専門知識を駆使して、どのような機器に適用するかに合わせてMOSFETの特性を精査する必要がある。

例えば、サーバ向け電源ユニットにおいてMOSFETをロードスイッチとして使う場合、そのスイッチは稼働時間のほぼ100%の間ずっとオン状態になる。そのためスイッチング特性はそれほど問題にならない。こうした用途向けのMOSFETを選ぶ際に重要になる性能指標は、オン抵抗(RDS(on))である。ただし、スイッチング電源などほかの用途では、MOSFETはアクティブスイッチとして使われるので、ユーザーはオン抵抗以外の性能パラメータも評価する必要がある。本稿では、MOSFETの具体的な用途をいくつか挙げ、それぞれにおいて重要度の高い特性を考察していく。

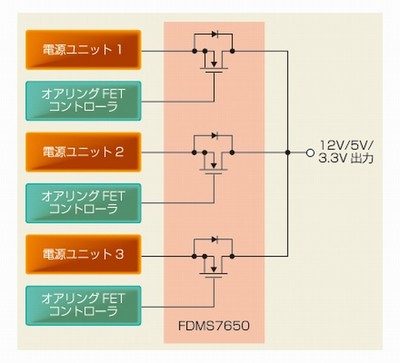

MOSFETの最も代表的な応用は、電源回路におけるスイッチング素子だろう。ただしMOSFETは、電源回路の出力部でも大きな役割を果たす。サーバや通信機器は通常、複数の電源ユニットを並列に接続したN+1段の冗長構成をとることで、電源障害によるダウンを避けて持続的な運用ができるように保証している(図1)。

並列接続した電源ユニットは、共通の負荷を分担して受け持つ。電源ユニットのうち1台が壊れても、システム全体としては継続的に稼働することが可能だ。ただしこうした構成では、複数の電源ユニットからの出力を1つにまとめながらも、故障した電源ユニットがほかの電源ユニットに影響を及ぼさないようにすることが不可欠になる。各電源ユニットの電力出力部にパワーMOSFETを挿入すれば、負荷を共有しながらも、電源ユニット同士を隔絶できる。こうした役割を担うMOSFETを「オアリングFET」と呼ぶ。複数の電源ユニットの電力出力を「論理OR(オア)」の形でまとめるからだ。

オアリングFETでは、MOSFETはスイッチとして動作する。ただし、サーバなどの装置では継続的な電力供給が必要になるため、このスイッチはほぼ常にオン状態になる。オンとオフを切り替えるスイッチ動作は、装置の運転開始時とシャットダウン時、電源ユニットに障害が起こった場合にしか基本的には発生しない。

オアリングFETを利用する機器においてMOSFET選択時に考慮すべき性能指標は、スイッチ動作を中心とした用途とは異なる。サーバの例では、通常の運用時にはMOSFETは導通状態で静止しており、機能的には単なる導体でしかない。従って、導通損失を最小化することが、オアリングFETを用いる設計者が最も配慮すべき点となる。

低オン抵抗で部品コストと基板サイズを低減

一般にMOSFETメーカーは、オン状態の抵抗値をRDS(on)として規定している。このRDS(on)は前述の通り、オアリングFETにおいて最も重要なデバイス特性である。データシートでは、ゲート・ソース間電圧(VGS)とスイッチを流れる電流値の両方をパラメータとしてオン抵抗を規定している。ただし、ゲート駆動電圧が十分に高い領域では、RDS(on)はほぼ一定の値をとる。例えば、フェアチャイルドセミコンダクターのnチャネルパワーMOSFET「FDMS7650」のデータシートは、ゲート駆動電圧が10Vのときにオン抵抗が最大0.99 mΩだと規定している。

電源装置の小型化とコストの最小化を図るなら、低オン抵抗はいっそう重要になる。電源装置の設計では、個々の電源ユニットごとに複数のオアリングMOSFETを並列に動作させる必要があることが多い。負荷が求める電流を供給するために複数のMOSFETを使う必要があるからだ。複数のMOSFETを並列に接続すれば、実効的にRDS(on)を削減できる。

思い出してほしい。DC(直流)回路では、抵抗を並列に接続すると、その合成抵抗値は必ず個々の抵抗値よりも小さくなる。例えば、2Ωの抵抗を2個並列に接続すると、合成抵抗は1Ωの抵抗1つ分に等しくなる。つまり、RDS(on)が小さく電流定格の大きいMOSFETを採用すれば、電源ユニットに使うMOSFETの点数を最少に抑えられる(オン状態の抵抗値を最小化する手法について詳しくは、本稿末尾の補足記事「RDS(on)を最小限に抑えるチップ/パッケージ設計技術」を参照)。

電源ユニットを設計する際には、RDS(on)のほかにもMOSFETの選択基準として重要なパラメータがいくつかある。設計時には多くの場合、データシートに記載された安全動作領域(SOA:Safe Operating Area)を精査しなければならない。SOAとは、MOSFETが安全に動作する電流と電圧の範囲を示すもので、ドレイン電流とドレイン・ソース間電圧を縦軸と横軸にとった平面に表す。

オアリングFET用途の場合、主に問題となるのは、「完全なオン状態」にあるFETの電流容量である。このドレイン電流の値は、実際にはSOAを参照しなくても分かる。もう一度FDMS7650を例に挙げよう。このMOSFETの定格電流は36Aであり、サーバ向けに用いられる一般的なDC-DC電源装置に適している。

ホットスワップ(活線挿抜)機能を実装する設計の場合には、SOAがさらに重要になる。ホットスワップを行う場合、MOSFETは「部分的にオン」の状態で動作しなければならない。SOAからは、パルス時間ごとの電流と電圧の限界値を読み取ることが可能だ。

前述の定格電流について言えば、温度パラメータも考慮する必要がある。MOSFETが常にオン状態にある場合は、熱の影響を受けるからだ。さらに、接合部温度が上昇すると、RDS(on)が増加してしまう。MOSFETのデータシートには、熱抵抗のパラメータも記載されている。この値は、MOSFETのパッケージが半導体の接合部から熱を逃す能力の高さを示す。熱抵抗値(RθJC)は、簡単に言えば、接合部からパッケージ間の熱抵抗と定義できる。

この点についてもう少し詳しく説明すると、データシートに記載されている通り、この測定値は実際には素子の接合部(縦型MOSFETではダイの表面付近)からパッケージの外面までの抵抗値を表している。

PowerQFN(PQFN)パッケージの場合は、パッケージ自体が大きなドレイン端子の中央部だと見なされる。従ってこの場合、RθJCはダイとパッケージからなる系の熱抵抗に相当する。一方でRθJAはダイ表面から外気までの熱抵抗に相当する。この値はプリント基板の設計によって変わるので、データシートでは通常、仕様値として記載したRθJAが得られるプリント基板の条件として、層数や銅めっきの厚さなどを注釈に示している。

要点を整理しよう。熱抵抗(RJC)はMOSFETのパッケージ技術によって決まるため、MOSFETを使ってパワーエレクトロニクス回路を設計するユーザー側では制御できない。フェアチャイルドセミコンダクターがパワーMOSFETに採用しているパッケージ「Power 56」のように、熱抵抗の特性を改善した最新のパッケージでは、熱抵抗は1℃/W〜2℃/Wに抑えられている。前述の36VパワーMOSFETのFDMS7650では1.2℃/Wだ。一方、接合部周囲間熱抵抗(RJA)は、プリント基板の設計によって変化する。そのため、熱設計を最適化すれば、信頼性を高めてシステムの平均故障間隔(MTBF:Mean Time Between Failure)を延ばすことが可能となる。

スイッチング電源に使われるMOSFET

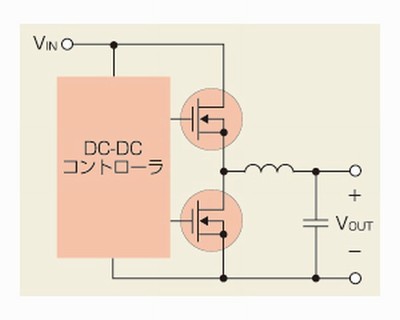

それでは次に、スイッチング電源について考察しよう。この用途に適したMOSFETを選ぶには、データシートのどの項目に注意すべきだろうか。MOSFETをスイッチング電源のスイッチング素子として使う場合、当然ながらそのMOSFETは定期的にオンとオフが切り変わる、スイッチング動作を繰り返す。スイッチング電源にはさまざまなトポロジがあるが、ここでは図2に示す簡単な例で考える。

図2の通り、DC-DC電源で一般的に使われる基本的な降圧型コンバータは、スイッチング機能を実現するために2つのMOSFETを使う。これらのスイッチング素子は、インダクタにエネルギーを蓄え、そのエネルギーを負荷に放出するという動作を交互に繰り返す。最近のスイッチング電源では、スイッチング周波数を数百kHzから、場合によっては1MHzを超える高い値に設定している。周波数を高めれば磁気部品の小型化と軽量化が可能になるためだ。

確かに電源の設計は複雑であり、MOSFETを評価する簡単な公式のようなものは無い。しかし、いくつかの重要なパラメータについて、なぜそれらのパラメータが重要なのかを考えてみたい。電源設計者の多くは従来、ゲートチャージ(QG)とRDS(on)を掛け合わせた値を性能指標としてMOSFETの特性を評価してきた。

ゲートチャージとオン抵抗は、ともに電源の効率に直接的な影響を与えるため重要となる。電源効率に影響する電力損失には、導通損失とスイッチング損失の2種類がある。

ゲートチャージは、スイッチング損失の主な要因となる。ゲートチャージは、MOSFETのゲート電流を充電および放電するために必要となるエネルギーで、大きさはナノクーロン(nC)で表わす。ゲートチャージとRDS(on)は、半導体の設計と製造の工程で互いに影響を及ぼし合う。一般的には、ゲートチャージが低ければ、オン抵抗はやや高くなる。

スイッチング電源にMOSFETを使う場合に、次に重要なパラメータは、出力静電容量、しきい値電圧、ゲート抵抗、そしてアバランシェエネルギーである。

これらのパラメータの重要性は、スイッチング電源のトポロジによって相対的に変化する。その一例として、同期整流方式をとる旧来型の降圧コンバータと、共振コンバータを比較してみよう。共振コンバータは、ドレイン・ソース電圧(VDS)またはドレイン電流(ID)がゼロ点を越えるときだけMOSFETをスイッチングすることで、スイッチング損失を最小化する。こうした技術は、ソフトスイッチングや、ゼロ電圧スイッチング(ZVS:Zero Voltage Switching)、あるいはゼロ電流スイッチング(ZCS:Zero Current Switching)と呼ばれる。このようなトポロジでは、スイッチング損失が最小化されるため、オン抵抗の重要性が比較的高まる。

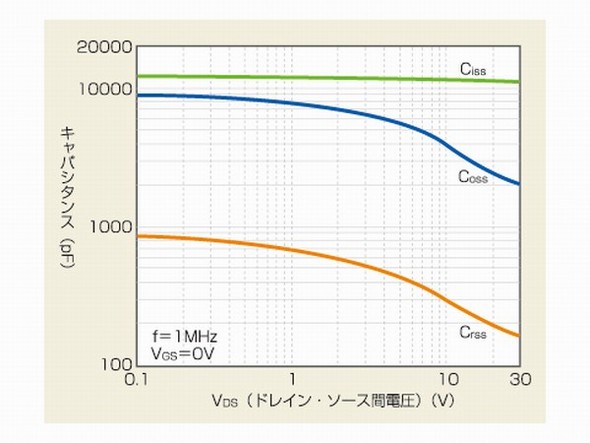

どちらのタイプのコンバータでも、出力キャパシタンス(COSS)値が小さい方が有利に作用する。共振コンバータの共振回路は、出力キャパシタンスとトランスの漏れインダクタンスの組み合わせによって変化する。さらに、共振回路は両方のMOSFETがオフになるデッドタイム(不感時間)の間に出力キャパシタンスを完全に放電しなければならない。そのため、共振トポロジでは出力キャパシタンスの値が低いことが重要となる。ここでは一例として図3に、前出のパワーMOSFETのFDMS7650の出力キャパシタンスとドレイン・ソース電圧の関係を示す。

旧来の降圧コンバータは、先に述べたソフトスイッチングコンバータと対比して、ハードスイッチングコンバータとも呼ばれることもある。この降圧コンバータでは、共振コンバータとは別の理由から出力キャパシタンスが小さい方が有利に作用する。出力キャパシタンスに蓄えられた電力は、共振コンバータでは再利用されるが、降圧コンバータではスイッチングのサイクルごとに失われてしまう。従って、同期整流方式の降圧コンバータでは、特にローサイド側スイッチの出力キャパシタンスが小さいことが重要になる。

モーター制御用途におけるMOSFET

パワーMOSFETが利用されるもう1つの用途にモーター制御がある。この用途では、最も重要な選択基準がこれまでに説明した用途とは異なる。モーター制御回路では、近年のスイッチング電源に見られるような高い周波数でのスイッチングは行わない。一般的なハーフブリッジ型制御回路にはMOSFETが2個(フルブリッジ型では4個)使われる。しかし、どちらのMOSFETもかなりの時間はオフになったまま、つまり不感時間となる。

このようなモーター制御用途において極めて重要なのが、逆回復時間(trr)だ。モーター巻き線などの誘導負荷を制御する際に制御回路によってブリッジ回路の一方のMOSFETがオフ状態に切り替わると、ブリッジ回路内のもう一方のMOSFETがボディダイオードを介して電流を一時的に逆方向に流す。こうして電流を再循環させることにより、モーターへの電力供給を維持している。このとき最初にオフにしたMOSFETを再度オンにする場合は必ず、このMOSFETを通して、もう一方のMOSFETのボディダイオードに蓄積されている電荷を除去して放電しなければならない。ここでエネルギー損失が発生する。逆回復時間が短ければ、このエネルギー損失を最小限に抑えられる。

本稿で解説した通り、MOSFETを電力回路に使用する場合には、まずその用途について熟考した上で、MOSFETの特性を評価する必要がある。MOSFETメーカーが訴求する特性ではなく、これから開発する機器に本当に必要な特性に着目して、優先すべき特性を見極めなければならない。

【補足記事】RDS(on)を最小限に抑えるチップ/パッケージ設計技術

設計者はたいていの場合、MOSFETの仕様を精査する過程で、設計に必要なスペックを把握している。ただし、半導体メーカーがMOSFETの動作特性を実現した手法について具体的に検証することが設計に役立つ場合もある。

ここでは、RDS(on)について考察してみよう。MOSFETの特性は、チップの設計やチップの製造プロセスだけで決まるわけではない。例えばオン抵抗では、オン状態の抵抗を最小限に抑えるためにパッケージ設計が極めて重要な役割を担っている。

オン抵抗は、導通損失に大きく関わるパラメータであり、導通損失にはパッケージ設計が大きな影響を及ぼす。従ってオン抵抗の特性は、パッケージ設計によって大きく左右される。本稿の本文で紹介したフェアチャイルドセミコンダクターのnチャネルパワーMOSFET「FDMS7650」のオン抵抗について検証してみよう。1mΩ以下という低いオン抵抗を実現した要因のうち、ほぼ半分はパッケージ設計にある。FDMS7650のパッケージは、通常であればアルミニウムや金のボンディングワイヤーを使う、ソース電極とリードフレームの接続に、大型の銅クリップを採用した。こうしたパッケージ技術によって、パッケージの抵抗を最小限に抑えられるだけでなく、スイッチング中にリンギングが発生する主要因となるソースのインダクタンスも低減している。

Profile

Mike Speed氏

Mike Speed氏は、Fairchild Semiconductorでセグメントマーケティングディレクタを務めている。エレクトロニクス業界で32年を超える経験を持つ。22年間にわたり電源装置のシステム設計・開発に携わったほか、10年間にわたってパワーアナログとパワーMOSFETの先端技術に専門的に取り組んでいる。同氏は、英国チェルムスフォードのChelmer Institute of TechnologyでHigher National Diploma(HND)を取得した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

図1 複数の電源を並列接続するN+1段の冗長構成にMOSFETを利用

図1 複数の電源を並列接続するN+1段の冗長構成にMOSFETを利用 図2 スイッチング電源アプリケーションではハイサイド/ローサイドのMOSFETをペアで使う

図2 スイッチング電源アプリケーションではハイサイド/ローサイドのMOSFETをペアで使う 図3 フェアチャイルドセミコンダクターのMOSFET「FDMS7650」のCOSS対VDS特性

図3 フェアチャイルドセミコンダクターのMOSFET「FDMS7650」のCOSS対VDS特性