ソフトウェア処理の複雑化に備えよ、プロセッサ性能の飛躍的向上が急務:プロセッサ/マイコン

「モバイル」「ワイヤレス」「ネットワーク」。これらのギガトレンドを背景に、エレクトロニクス業界が今後取り組んでいくアプリケーションを見据えると、プロセッサの性能と効率の飛躍的な向上が急務だ――。半導体チップに集積するプロセッサ回路をIPコアとして供給するベンダー各社から今、こうした指摘が相次いでいる。

「モバイル」「ワイヤレス」「ネットワーク」。これらのキーワードは、いずれもエレクトロニクス業界の「ギガトレンド」である。象徴的なのはスマートフォンやタブレットPCだろう。しかしそれだけではない。インフラ機器から産業/ビジネス機器、消費者機器に至るまで、この潮流はさまざまな分野の多くの機器に、あらがい難く押し寄せている。

例えば、通信ネットワークのインフラ機器では、モバイル端末からのインターネット利用を起爆剤としたトラフィックの急拡大に、喫緊の対応を迫られている。ビジネス機器の領域では、インターネット経由で遠隔地をつなぐビデオ会議システムの改善が進んでおり、映像品位の向上に加えて、今後は顔認識や音響効果といった機能を取り込んでいく。消費者機器では、テレビをはじめとするホームエンタテインメント機器でネットワーク接続機能の搭載が進む。さらに、そうした機器をワイヤレスでメディアサーバとつなぐ提案もある。戸外に目を向ければ、自動車はいまやワイヤレスでネットワークにつながるモバイル機器へと進化を遂げつつある。

ソフトウェア処理が大幅に複雑化へ

図1 Tensilicaのクリス・ローウェン氏 同社のファウンダーで、CTOを務めている。半導体関連企業の首脳陣が集う報道関係者向けイベント「Globalpress Electronics Summit 2011」(米国カリフォルニア州のサンタクルーズで2011年3月28〜31日に開催)で新型プロセッサコアについて発表した。

図1 Tensilicaのクリス・ローウェン氏 同社のファウンダーで、CTOを務めている。半導体関連企業の首脳陣が集う報道関係者向けイベント「Globalpress Electronics Summit 2011」(米国カリフォルニア州のサンタクルーズで2011年3月28〜31日に開催)で新型プロセッサコアについて発表した。このようなギガトレンドを背景に、エレクトロニクス業界が今後取り組んでいくアプリケーションを見据えると、1つの大きな課題が浮かび上がる。すなわち、プロセッサの性能と効率を飛躍的に高めなければならない――。半導体チップに集積するプロセッサ回路をIPコアとして供給するベンダー各社から今、こうした指摘が相次いでいる。その理由はこうだ。

「われわれが今後のアプリケーションで直面する問題は、非常に複雑なものになる。それらを解決するには、ソフトウェアによるプログラマビリティが不可欠だ。それも、これまでのプロセッサではとうてい届かないレベルのコンピューティング性能が必要になる。性能と効率の両面で、飛躍的な向上が求められる」(TensilicaのファウンダーでCTOを務めるクリス・ローウェン(Chris Rowen)氏)(図1)。

図2 MIPS Technologiesのアート・スイフト氏 マーケティング担当バイスプレジデントを務めている。「Globalpress Electronics Summit 2011」で次世代プロセッサコアの発表に臨んだ。

図2 MIPS Technologiesのアート・スイフト氏 マーケティング担当バイスプレジデントを務めている。「Globalpress Electronics Summit 2011」で次世代プロセッサコアの発表に臨んだ。「ソフトウェアシステムはどんどん複雑になっていく。例えば、データレートの向上はとどまらず、ネットワークを流れるパケットをこれまで以上に精査するようになっている。モバイル機器では、ベースバンドでより高いデータレートのモデム処理が求められている。また、モバイル機器のみならずホームエンタテインメント機器でも、Javaベースのアプリケーションを実行する必要が生じている」(MIPS Technologiesのマーケティング担当バイスプレジデントを務めるArt Swift(アート・スイフト)氏)(図2)。

マルチスレッドの64ビットコアが解に

さらにMIPS Technologiesは、前述のような要件に応えるためには、「ソフトウェアシステムのメモリ容量を拡大し、これまでよりも大幅に高い処理性能を達成しなければならない」(スイフト氏)と指摘する。しかも、「消費電力はできるだけ小さく、チップ面積はなるべく小さく、チップに外付けする部品は低コスト品が使えるようにしなければならない」(同氏)という。

そこで同社は、これらの要件を満たす次世代プロセッサIPコアとして、マルチスレッド対応の64ビットプロセッサコア「Prodigy(開発コード)」を開発し、2011年後半に正式リリースする計画だ。2011年3月28日に発表した。通信/ネットワーク機器やストレージ装置、モバイル機器など、さまざまな組み込み機器に搭載するチップに使えるという。シングルコア構成とマルチコア構成のいずれにも対応可能である。「64ビットのマルチスレッド対応プロセッサIPは、業界初だ」(スイフト氏)と主張する。

実際に同社自体も、64ビットコアとしては、1991年に「MIPS R4000」を発表しており、その後64ビットアーキテクチャ「MIPS64」に基づくコアを供給しているが、マルチスレッドには対応していなかった。同社既存のマルチスレッド対応コアは、32ビットアーキテクチャ「MIPS32」に基づくシングルコア品の「MIPS32 34K」やマルチコア品の「MIPS32 1004K」などに限られていた。

「効率」にはマルチスレッドが有効

MIPS Technologiesが64ビットの次世代コアと位置付けるProdigyの開発に当たってまず問題視したのは、単にプロセッサの処理性能を高めるだけでなく、「効率」も向上させる必要があるという点だ。

ここで同社が言う効率とは、例えば処理性能当たりの消費電力を指す。処理性能が高まったとしても、回路規模が大幅に増えてリーク電流に起因する待機時の消費電力が大きくなってしまったり、クロック周波数を引き上げることで動作時の消費電力が増えてしまったりしては、今後のアプリケーションで求められる要件には応えられない。そこで効果を発揮するのがマルチスレッド技術だと同社は主張する。その理由はこうだ。

一般に、消費電力の制約が厳しい状況下でプロセッサの処理性能を高めるには、並列化が有効である。ただし並列化と一口に言っても、実際にはさまざまな手法が存在する。

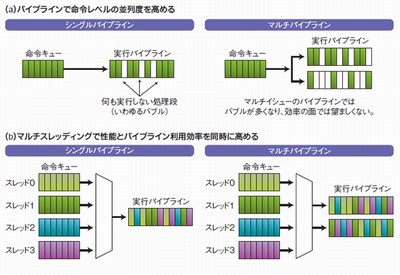

例えば、命令レベルの並列度を高める基本的な手法の1つに、命令パイプラインがある。命令の処理回路を複数段、直列につないだパイプラインを用意し、命令列を順次投入することで、各段で並列に処理を実行する。複数本のパイプラインを設けて複数の命令を同時発行する(マルチイシュー)ことで並列度を高める手法もあるが、「パイプライン中のバブル(何も実行しない処理段)が比較的多くなるので、パイプラインの使用効率については低くなってしまう。命令の発行順序を組み替えるアウトオブオーダー実行を使えば、バブルの発生自体は抑えられる。ただしそれは、回路規模と消費電力の大幅な増加と引き換えになる」(MIPS Technologies)。

これに対し、同社によれば、マルチスレッディングを採用すれば、パイプラインが1本の構成でも、処理性能とパイプライン使用効率の両方を大幅に高められる(図3)。さらに、マルチイシューのパイプラインに同時マルチスレッディング(SMT:Simultaneous Multi-Threading)を適用すれば、アウトオブオーダー実行や投機実行といった消費電力の大きな仕組みの規模を低減しながらも、いっそう高い性能を実現することが可能になると説明する。

マルチスレッディングに対応する同社のプロセッサコアでは、「VPE(Virtual Processing Element)」と呼ぶ仮想プロセッサを追加したり、パイプラインの本数を増やしたりすることで、回路規模の増大とそれに起因するリーク電流の増加を最小限に抑えつつ、同じクロック周波数で処理性能を大幅に高められるという。実際に、64ビットコアのProdigyでは、32ビットコアの1004Kに比べて、処理性能を飛躍的に高めながらも、効率も改善できるという。「パイプラインの段数を増やしたり、投機実行を組み込んだりして処理性能を高める手法では、回路規模が大きくなってリーク電流が増える上、クロック周波数を高める必要があり動作時の消費電力も大きくなるので、効率については低下してしまう」(同社)。

図3 マルチスレッディングで性能と効率を両立 (a)は命令パイプラインの概念図である。パイプラインの段数を増やせば、命令レベルの並列度は高まる。マルチパイプライン化すれば、性能はさらに改善できるものの、バブルが多くなるので、対策無しでは効率が大幅に低下してしまう。(b)はMIPS Technologiesが提唱するマルチスレッディング手法である。シングルパイプラインの効率をいっそう高められる上、マルチパイプライン化して同時マルチスレッディング(SMT)を適用すれば、性能をさらに向上させることが可能だ。出典:MIPS Technologies

図3 マルチスレッディングで性能と効率を両立 (a)は命令パイプラインの概念図である。パイプラインの段数を増やせば、命令レベルの並列度は高まる。マルチパイプライン化すれば、性能はさらに改善できるものの、バブルが多くなるので、対策無しでは効率が大幅に低下してしまう。(b)はMIPS Technologiesが提唱するマルチスレッディング手法である。シングルパイプラインの効率をいっそう高められる上、マルチパイプライン化して同時マルチスレッディング(SMT)を適用すれば、性能をさらに向上させることが可能だ。出典:MIPS Technologies64ビットで無限のメモリ空間を得る

効率の問題に続いてMIPS Technologiesが着目したのは、メモリ空間である。マルチスレッディングによって並列に実行するタスクの数が劇的に増えるので、所要の物理メモリの量も一気に拡大する。そこで顕在化するのが、プロセッサコアのアーキテクチャによって決まってしまうメモリアドレス空間の上限だ。32ビットプロセッサでは、アクセス可能な物理アドレス空間は最大4Gバイト(2の32乗のアドレス空間に相当)に限られる。同社は「ハイエンドの組み込みアプリケーションでは、32ビットはもはや不十分だ」と指摘する。

同社によれば、ネットワーク分野のアプリケーションの多くは、すでに64ビットアーキテクチャをベースにしているという。また、「現在のセットトップボックス(STB)やデジタルテレビ、携帯電話機、タブレットは、ギガバイト単位のメモリを搭載している。今後登場するアプリケーションで求められるメモリ空間は、32ビットプロセッサの制約である4Gバイトを超えてしまうだろう」(同社)。64ビットアーキテクチャに移行することで、アクセス可能な物理アドレス空間を実効的にほぼ無制限に拡大できるようになる。

MIPS Technologiesは、Prodigyの具体的な仕様や性能を2011年4月末の時点では公表していないが、同コアのリリース計画の発表資料の中で、「MIPS32アーキテクチャとMIPS64アーキテクチャの間のシームレスなコードの互換性と洗練された上位互換性を提供する」と述べており、同社既存の32ビットコアとバイナリレベルの互換性を確保するとしている。2011年後半の正式リリースの際に、詳細仕様やベンチマーク結果を公表する予定だという。

命令長とメモリ入出力幅を拡張

Tensilicaは、ユーザーがカスタマイズ可能なコンフィギュラブル・プロセッサコアを供給するベンダーである。プロセッサコア生成ツールソフトウェアの形態でユーザーに提供しており、ユーザーはそのツールを使ってプロセッサコアの命令セットや周辺機能を手元でカスタマイズした上で、そのコアの設計データを生成することが可能だ。

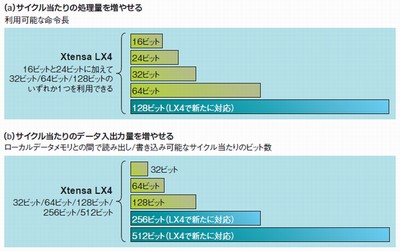

同社のCTOを務めるクリス・ローウェン氏は、前述の通り、今後のソフトウェア処理には「性能と効率の両面で、飛躍的な向上が求められる」と指摘している。そこで同社が提供するのは、動画像やネットワーク処理の他、有線/無線通信のベースバンド処理などを想定し、大量かつ高速のデータ処理を主なタスクとする用途に向けて最適化したプロセッサコア「Xtensa LX4」である。2011年3月28日に発表した。「主要な早期顧客に対しては、すでに2011年10月から提供を開始している」(ローウェン氏)。

同社はこのようにデータ処理用途に最適化したプロセッサコアを「データプレーン・プロセッサ(DPU)」と呼ぶ。新型コアのXtensa LX4では、同社従来のDPUである「Xtensa LX3」に比べてローカルデータメモリとの入出力帯域幅を4倍に拡張した上、可変長のFLEX命令(Flexible Length Instruction eXtensions)の上限を従来の64ビットから128ビットへと引き伸ばした(図4)。これらの改善により、「従来に比べて、負荷が4〜8倍も高いタスクに対応できる」(ローウェン氏)と主張する。

Xtensa LX4の動作周波数とチップ上の専有面積については、45nm世代の高性能半導体製造プロセス技術を適用した場合、基本的なコア構成でそれぞれ1GHz以上、0.044mm2になるという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増