「2倍の入出力帯域、5倍のDSP、60%省電力」、Alteraが描く20nm世代FPGA:プログラマブルロジック FPGA(1/2 ページ)

FPGA大手のAlteraが20nm世代の半導体プロセスで製造する次世代FPGAに向けて開発中の技術の概要を明らかにした。超高速シリアルトランシーバと、3次元実装パッケージ、可変精度のDSPブロックの3つである。製品化の時期は2013年で、製品としての具体的な仕様はあらためて発表するという。

「20nm世代のFPGAは、通信/ネットワーク機器をはじめとしたハイエンドのエレクトロニクスシステムを統合し、実装するための究極のプラットフォームになる」――。FPGA大手ベンダーのAltera(アルテラ)は、20nm世代の半導体プロセスで製造する次世代FPGAに向けて開発中の技術の概要を発表した。(1)超高速シリアルトランシーバと、(2)3次元実装パッケージ、(3)可変精度のDSP(デジタル信号処理)ブロックの3つの技術である。

これら3つの技術を適用することで同社の20nm世代FPGAは、28nm世代のハイエンドファミリ「Stratix V」の最大規模品に比べて、単一パッケージで入出力信号の総帯域幅が2倍以上、システムの統合性が10倍以上、DSP性能が5倍以上に高まるという。さらに、消費電力については、低電力化に主眼を置いて最適化すれば最大60%の削減が可能だとする。

同社でSenior Vice President and Chief Technology Officer(CTO)を務めるMisha Burich氏は、「既に、主要なユーザーと20nm世代のFPGAに求められる要件などについて話し合っている」としており、今後は2013年第2四半期にも20nm世代品のエンジニアリングサンプルの出荷を始めて、同年末までに量産を開始する見通しだという。さらに、20nm世代品に対応したFPGA開発ツールについては、FPGA自体の出荷に先駆けて2013年第1四半期に提供を開始する計画だ。ただ、これらは現時点での予定であり、具体的なスケジュールについては、今後あらためて発表するという。

Alteraが20nm世代で導入する新技術の効果をまとめたスライドである。なお同社は、20nm世代でも現行の28nm世代と同様に、製造についてはTSMCに一社に委託する方針だ。出典:日本アルテラ (クリックで画像を拡大)

Alteraが20nm世代で導入する新技術の効果をまとめたスライドである。なお同社は、20nm世代でも現行の28nm世代と同様に、製造についてはTSMCに一社に委託する方針だ。出典:日本アルテラ (クリックで画像を拡大)高速シリアルはチップ間で40Gbps、バックプレーン経由で28Gbpsへ

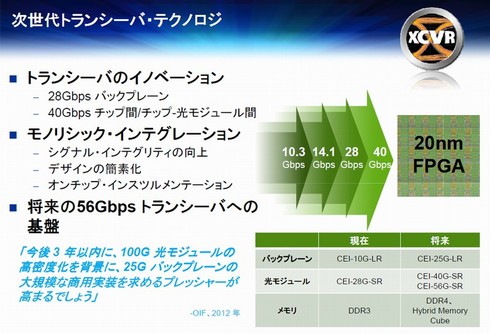

Alteraが20nm世代のFPGAで導入する3つの技術のうち、1つ目の超高速シリアルトランシーバについては、最大40Gビット/秒動作を実現するという。「既にテストチップが手元にあり、特性の評価を進めている」(CTOのBurich氏)。単一のボード上に実装したFPGAと周辺チップを直接つなぐ、チップ間インタフェースに向けたトランシーバである。現行の28nm世代品では、同用途のトランシーバで最大28Gビット/秒にとどまっていた。

さらに、20nm世代品のこの40Gビット/秒トランシーバは、電気的な配線を介したチップ間接続に加えて、光/電気変換機能を備える光トランシーバモジュールを介した光インタフェースにも応用でき、OIF(Optical Internetworking Forum)が定める共通仕様「CEI-40G」の「SR(Short Reach)」に準拠するという。現行品は「CEI-28G-SR」までしか満たせなかった。

この他に20nm世代品では、バックプレーン経由の接続に向けた28Gビット/秒動作のトランシーバも用意する。OIF仕様の「CEI-25G-LR(Long Reach)」に準拠する。現行品は14.1Gビット/秒が上限で、「CEI-10G-LR」までしか対応できなかったという。

20nm世代では、FPGAに集積する高速シリアルトランシーバの動作速度を向上させ、チップ間インタフェース用で40Gビット/秒、バックプレーン経由の接続用で28Gビット/秒を実現するという。出典:日本アルテラ (クリックで画像を拡大)

20nm世代では、FPGAに集積する高速シリアルトランシーバの動作速度を向上させ、チップ間インタフェース用で40Gビット/秒、バックプレーン経由の接続用で28Gビット/秒を実現するという。出典:日本アルテラ (クリックで画像を拡大)なおAlteraは、これらの超高速シリアルトランシーバをFPGAのチップに混載する方針だ。すなわち同社は、トランシーバをFPGAとは材料やプロセスが異なる製造技術で用意して、パッケージ内で支持基板を介してFPGAチップに接続するという手法はとらない。「FPGAのロジックエレメントを集積する1枚のチップに混載した方が、高いシグナルインテグリティ(信号品質)が得られるなど、メリットが大きいと判断した」(Burich氏)。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

AlteraのCTOを務めるMisha Burich氏が来日した機会に聞いた。

AlteraのCTOを務めるMisha Burich氏が来日した機会に聞いた。