ARMから見た7nm CMOS時代のCPU設計(3):福田昭のデバイス通信(14)(1/2 ページ)

今回から、ARMの講演の本論に入る。論理設計から、シリコンダイに落とし込むまでに焦点を当てる。LSI設計で最も重要なのは、論理合成と配置、配線である。これらの設計品質が、“シリコンダイ”の良しあしを決める。

トランジスタ性能をシリコンダイに落とし込む(続)

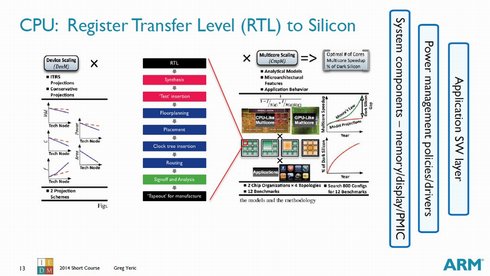

ARMの設計技術者による講演は、今回から本論に入っていく。それはトランジスタの性能トレンドを把握しつつ、その性能を維持しながら、SoC(System on a Chip)のシリコンダイに落とし込むことだ。すなわち論理設計とトランジスタ設計の仲介である。もう少し具体的に述べると、SoCの回路に実行させたいことを、一定の様式(記述言語)にしたがって記述し、最終的にはシリコンのトランジスタアレイによって具現化する作業である。

シリコンに最も近い回路の記述方法は、論理ゲートで回路を記述することである。AND(論理積)ゲートやOR(論理和)ゲートなどによって回路を記述する。しかし現在の大規模なSoCを論理ゲートで記述することは、現実的ではない。作業量があまりに膨大になってしまうからだ。そこで、論理ゲートよりも抽象的な記述であるRTL(レジスタ転送レベル)記述で、回路を記述する。RTL記述では、レジスタが変数であり、クロックごとにレジスタの振る舞いを記述していく。かなり面倒な作業なのだが、それでも論理ゲートを記述することに比べると、作業量はずっと少ない。

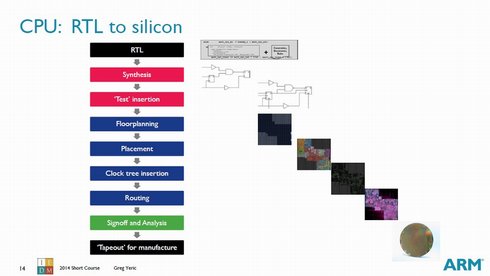

トランジスタレベル(左端)と、シリコンダイレベル(右中央)を結びつける。その工程(左中央のフローチャート)がLSI設計である。LSIの具体的な設計作業は、回路の動作をRTLで記述することから始まる(クリックで拡大) 出典:ARM

トランジスタレベル(左端)と、シリコンダイレベル(右中央)を結びつける。その工程(左中央のフローチャート)がLSI設計である。LSIの具体的な設計作業は、回路の動作をRTLで記述することから始まる(クリックで拡大) 出典:ARMRTL記述からシリコンの製造データまで

RTLで回路を記述するためには、普通はハードウエア記述言語(HDL:Hardware Description Language)を利用する。HDLのルールに従ってRTLで記述した回路を、論理合成ツールに入力することで、論理ゲートで記述した回路(ネットリスト)が出力として得られる。

ネットリストを実際のシリコンにトランジスタレベルで埋め込む、仮想的な作業はここから始まる。最初は回路の配置(プレイスメント)である。複雑で大規模な回路の場合は、あらかじめ、おおまかな配置(フロアプラン)を決めておくこともある。配置の次は、クロック配線のレイアウトに入る。それから、信号配線を引き回す(ルーティング)。いずれも設計ツールの支援を受けながら、作業を進める。

設計と検証が完了すると、サインオフ(設計から製造に移行するための手続き)となる。サインオフが済むと、設計データをシリコン製造用のマスクデータに変換(テープアウト)し、シリコンダイの製造へと進む。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」