EE Times Japan >

プロセス技術 >

ARMから見た7nm CMOS時代のCPU設計(3):福田昭のデバイス通信(14)(2/2 ページ)

» 2015年03月24日 09時00分 公開

[福田昭,EE Times Japan]

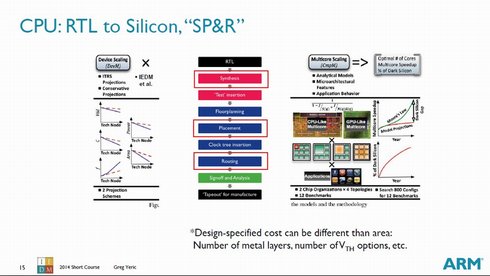

論理合成、配置、配線が重要

これらの一連の工程の中で、最も重要なのは論理合成(シンセシス)と配置(プレイスメント)、配線(ルーティング)である。これらの設計品質が、「シリコンダイの良しあし」を大きく左右するからだ。「シリコンダイの良しあし」とは、動作性能(動作周波数や消費電力など)や製造余裕(製造ばらつきに対する強さ)、シリコンダイ面積などを指す。

論理合成と配置、配線の工程では、設計の結果が要求仕様を満たせないことがある。その場合、工程はやり直し(イタレーション)になる。要求仕様の水準がきわめて高いときには、設計のやり直しを繰り返すことが珍しくない。設計の各工程におけるやり直しは、製造のやり直しよりも、はるかに低いコストで済むからだ。

CPU設計(RTLからシリコンまでの工程)で重要なのは、論理合成(シンセシス)と配置(プレイスメント)、配線(ルーティング)である。なお設計のコストを左右するのは、シリコン面積よりも、配線の層数やしきい電圧のオプション数などの制約条件になりがちである(クリックで拡大) 出典:ARM

CPU設計(RTLからシリコンまでの工程)で重要なのは、論理合成(シンセシス)と配置(プレイスメント)、配線(ルーティング)である。なお設計のコストを左右するのは、シリコン面積よりも、配線の層数やしきい電圧のオプション数などの制約条件になりがちである(クリックで拡大) 出典:ARM(次回に続く)

関連記事

ルネサスがマイコン用電源ICの決定版「かんたん電源IC」のラインアップを拡充

ルネサスがマイコン用電源ICの決定版「かんたん電源IC」のラインアップを拡充

ルネサス エレクトロニクスは2014年8月19日、マイコンへの電源供給用ICとして、設計の煩わしさを解消する複数の機能を盛り込んだ「かんたん電源ICシリーズ」の第2弾製品群のサンプル出荷を開始した。ルネサス製のマイコンや産業用SoCに最適な電源ICとして、広く提案していく。 半導体市場、2014年以降は緩やかに成長――IC Insightsが予測まとめ

半導体市場、2014年以降は緩やかに成長――IC Insightsが予測まとめ

IC Insightsが2014年の秋季予測を発表した。それによれば、2014年以降の半導体市場は堅調だが大きな成長は期待できないという。ファウンドリ市場でのシェアの低下に頭を悩ます中国は、今後はファブレス企業の設立に力を入れていくとしている。 用途によって変わるMOSFETの選択基準

用途によって変わるMOSFETの選択基準

MOSFETは成熟した電子デバイスなので、品種の選定は一見簡単なように思える。確かにユーザーは、MOSFETのデータシートに記載されている性能指標(Figure of Merit:FOM)についてはよく理解している。ただし実際の品種選びでは、エンジニアが専門知識を駆使して、どのような機器に適用するかに合わせてMOSFETの特性を精査する必要がある。 グラフェン+半導体ポリマーの“ハイブリッド素材”、高性能な有機トランジスタ実現の鍵に

グラフェン+半導体ポリマーの“ハイブリッド素材”、高性能な有機トランジスタ実現の鍵に

スウェーデンの大学とスタンフォード大学が、単層グラフェン上に半導体ポリマーが形成された“ハイブリッド素材”を開発。シリコンに匹敵する性能を持つ有機トランジスタの実現にまた一歩近づいた可能性がある。 微細化の限界に挑む、Siと新材料の融合で新たな展望も

微細化の限界に挑む、Siと新材料の融合で新たな展望も

半導体製品、特にSi(シリコン)材料を使ったトランジスタの歴史を振り返るとき、「微細化」が重要なキーワードであることは間違いない。微細化に伴って、50年あまりの間にトランジスタの処理性能は劇的に高まり、寸法は小さくなった。ところが、2000 年代に入り、状況が変わってきた。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

Special SitePR

あなたにおすすめの記事PR