不揮発性パワーゲーティング、メニーコアプロセッサの待機電力削減に威力:新技術(1/2 ページ)

東京工業大学(東工大)像情報工学研究所の菅原聡准教授らの研究グループと神奈川科学技術アカデミー(KAST)は、不揮発性パワーゲーティング(NVPG)がメニーコアのプロセッサやSoCの待機時電力削減に極めて有効なアーキテクチャであることを実証した。

東京工業大学(東工大)像情報工学研究所の菅原聡准教授らの研究グループは2015年3月、不揮発性パワーゲーティング(NVPG)がメニーコアのプロセッサやSoCの待機時電力削減に極めて有効なアーキテクチャであることを、神奈川科学技術アカデミー(KAST)と共同で実証した。

高性能PC/サーバー向けマイクロプロセッサや、最新のスマートフォン/タブレット端末向けSoCなどでは、処理性能の向上とともに待機時に消費するスタンバイ電力が増大し、大きな課題となっている。このスタンバイ電力を削減する方法として、菅原准教授や周藤悠介特任助教、山本修一郎特任教授らの研究グループが提案するNVPGや、それとは別のノーマリオフ(NOF)といったアーキテクチャが注目されている。

電源を遮断する時のみ不揮発記憶

NVPGは、電源を遮断してもメモリ内のデータを保持できるように、双安定記憶回路(SRAMやフリップフロップなど)に不揮発性メモリ素子を付加した回路構成をとる。特に、CMOSロジックが通常動作する場合には、不揮発記憶を用いずに通常の双安定記憶回路として動作する。電源を遮断する時のみ不揮発記憶を行うのが特長である。このため、通常動作には影響を与えず、効率よく待機時の電力削減を可能とする。

これに対して、NOFは常に不揮発記憶でデータを保持する。通常は電源を遮断しておき、必要な時だけ記憶回路に通電して、待機時の電力消費を抑える。この方法だと、データを記憶させるためにより多くの電力を消費し、動作速度が遅い、といった課題があった。

東工大の研究グループとKASTは、メニーコアのプロセッサやSoCにおける上位階層のキャッシュメモリへの応用を想定して、NVPGとNOFについてエネルギー性能の解析/定量評価を行った。特に今回は、NVPGとNOFのいずれも、不揮発性双安定記憶回路には東工大の研究グループが提案している不揮発性SRAM(NV-SRAM)を用いて回路を構成した。これまで評価されてきたNVPGとNOFは、異なる不揮発性記憶回路を用いていたが、今回はその影響を取り除くために同一のNV-SRAMを採用した。

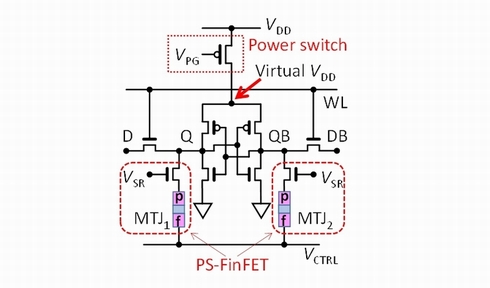

NV-SRAMは、通常のSRAMセルにトランジスタを介して、不揮発性メモリ素子である強磁性トンネル接合(MTJ)を接続した。このトランジスタによって、通常動作時にはMTJをSRAMから電気的に切り離す。また、NV-SRAMに接続されたパワースイッチでセルへの電源遮断を行う。

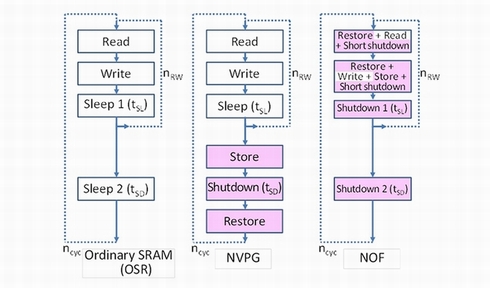

実際の評価作業として、NVPGでは電源遮断を行う時だけMTJへの書き込みを行い、待機時間が短い時はスリープモードの状態とした。NOFではデータ書き込み時には常にMTJへの書き込みを行い、待機時および毎回の読み出し後と書き込み後に電源を遮断した。比較のために、通常のSRAMが待機時には全てスリープモードとした。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- パワー停滞も光デバイス堅調、三菱電機の半導体部門