ARMから見た7nm CMOS時代のCPU設計(11)〜回路の遅延時間を変動させるさまざまな要因:福田昭のデバイス通信(22)(1/2 ページ)

今回は、回路の遅延時間を左右する要因について紹介する。例えば、コンタクト抵抗、しきい電圧、電源電圧、温度などがある。しきい電圧と温度、電源電圧と温度が遅延時間に与える影響はかなり複雑だが、その対処法として、DVFS(Dynamic Voltage and Frequency Scaling)技術が挙げられる。

微細化によってコンタクト抵抗の影響が増加

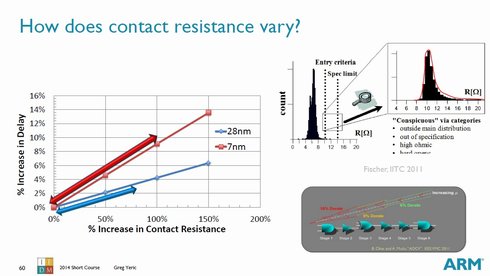

トランジスタやコンタクト、金属配線などの寄生素子である「抵抗(R)」と「静電容量(C)」は、回路の遅延時間を大きく左右する。微細化が進むと、これらRとCの変化が遅延時間に与える影響が変化する。

例えばコンタクト抵抗である。28nm世代の回路では、コンタクト抵抗が2倍に増えたときに遅延時間は4%ほど長くなった。これが7nm世代の回路になると、コンタクト抵抗が2倍に増えたときの遅延時間の増大は、約9%に悪化する。遅延時間の増加を4%に抑えるためには、コンタクト抵抗の増大を1.5倍にとどめておかなければならない。

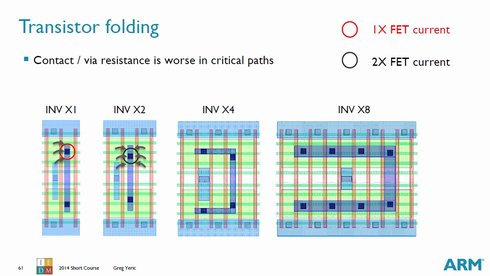

コンタクト抵抗の影響は、物理的なレイアウトによっても変わる。例えばインバータ回路である。最も小さなレイアウトの場合、1個のトランジスタの電流を1個のコンタクトが引き受ける。ところがゲートピッチを増やして電流駆動能力を高めたレイアウトだと、1個のコンタクトが2個のトランジスタの電流を受け持つことになる。コンタクト抵抗が増加することによる信号電圧への影響は、2倍に増える。

セルの幅とコンタクトの関係。セルの幅が最小単位(左端のレイアウト)のときは、1個のコンタクトが1個のトランジスタ電流を引き受ける。しかしセルの幅を広く確保すると、1個のコンタクトは2個のトランジスタによる電流を受け持つようになる(クリックで拡大) 出典:ARM

セルの幅とコンタクトの関係。セルの幅が最小単位(左端のレイアウト)のときは、1個のコンタクトが1個のトランジスタ電流を引き受ける。しかしセルの幅を広く確保すると、1個のコンタクトは2個のトランジスタによる電流を受け持つようになる(クリックで拡大) 出典:ARMしきい電圧と電源電圧、温度が遅延時間に与える影響

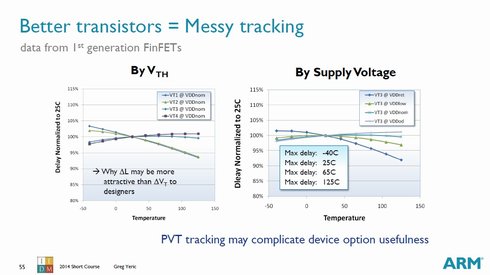

トランジスタのしきい電圧(VTH)と温度が遅延時間に与える影響と、電源電圧(VDD)と温度が遅延時間に与える影響は、かなり複雑な様相を呈する。第1世代のFinFETの事例を、ARMはスライドで見せていた。

電源電圧(VDD)を一定にしてしきい電圧(VTH)を変えると、遅延時間の温度依存性が大きく変化する。あるしきい電圧だと、低温では遅延時間が長く、高温では遅延時間が短くなる。ところが別のしきい電圧だと、低温では遅延時間が短く、高温では遅延時間が長くなる。しきい電圧の違いにより、逆の温度特性を示すようになる。

しきい電圧(VTH)を一定にして電源電圧(VDD)を変えると、この場合も遅延時間の温度依存性が大きく変化する。温度上昇によって遅延時間が短くなるVDDと、逆に温度上昇によって遅延時間が長くなるVDDがある。4通りのVDDで温度特性を調べると、遅延時間が最大になる温度は−40℃、+25℃、+65℃、+125℃と4通りになる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増