ARMから見た7nm CMOS時代のCPU設計(20)〜まとめ:CPU設計の将来像:福田昭のデバイス通信(31)(1/3 ページ)

シリーズ最終回となる今回は、これまでの内容をまとめてみよう。トランジスタの将来像から、消費電力と性能のバランスの取り方、微細化(スケーリング)の余地の拡大まで、ひと通り振り返る。

トランジスタ、配線、メモリの微細化が困難に

ARMが7nm CMOS時代のCPU設計を解説した講演の紹介レポートも、今回が最終回になる。講演は最後のまとめに入った。まず、講演の途中で小さなまとめとして挿入した講演スライド5枚を、再掲した。

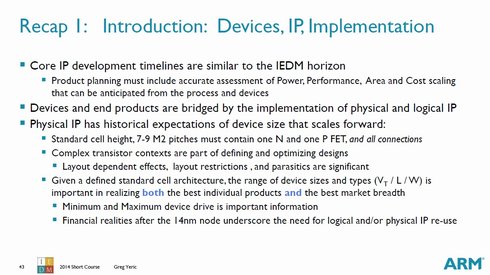

初めの講演スライドでは、IEDMの発表が次々世代以降のCPU開発でトランジスタ選択を決める重要な指針であることを示すとともに、物理設計の基本となるスタンダードセルのレイアウトとデバイス寸法の関係を説明した。

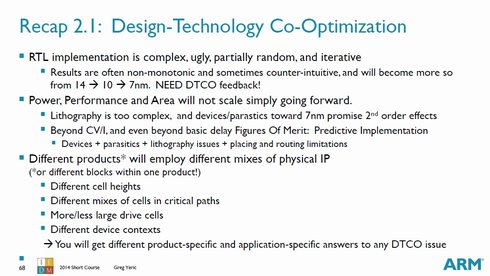

次のスライドでは主に、論理設計と物理設計の協調設計による最適化が、14nm世代以降のCPU設計では必須になることを示した。電流駆動能力の大きなセルや高さの違うセルなど、目的に合わせて数種類のスタンダードセルを使い分けていく。

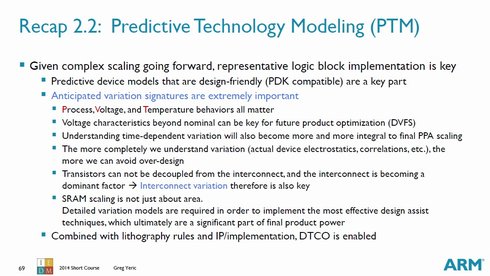

3枚目のスライドでは、今後の物理レイアウトを支えるPTM(Predictive Technology Modeling)を説明した。プロセスのばらつき、電源電圧の変動、温度の変動の、重要な3つの変動要因に対処する必要がある。またトランジスタのばらつきよりも、多層配線のばらつきが半導体チップの性能を左右するようになる。

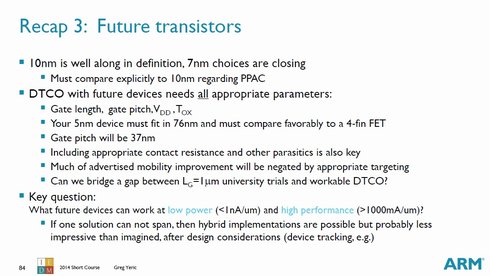

4枚目のスライドでは、10nm世代以降のトランジスタの姿を展望した。LSI設計では論理設計と物理設計の協調があらゆるパラメータに及ぶようになる。高いキャリア移動度を備えるチャンネル材料の採用が現実味を帯びてくる。

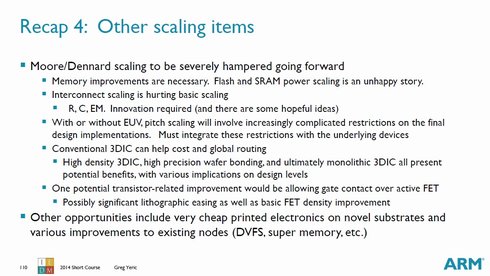

5枚目のスライドでは、トランジスタ以外の微細化(スケーリング)に関わる諸問題を取り上げた。フラッシュメモリとSRAMの微細化、多層配線の微細化は、いずれも困難になる。既存技術である3次元ICは助けにはなるものの、根本的な解決方法ではない。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ローム・東芝・三菱電機のパワー半導体はどうなるか

- 「Rapidusの隣」に光電融合パッケージ開発拠点、28年度の完成目指す

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」