EE Times Japan >

プロセス技術 >

ナノワイヤと非シリコン材料で「ムーアの限界」を突破:福田昭のデバイス通信 IEDM 2015プレビュー(6)(2/3 ページ)

» 2015年11月13日 10時30分 公開

[福田昭,EE Times Japan]

トランジスタの3次元構造を原子レベルで把握

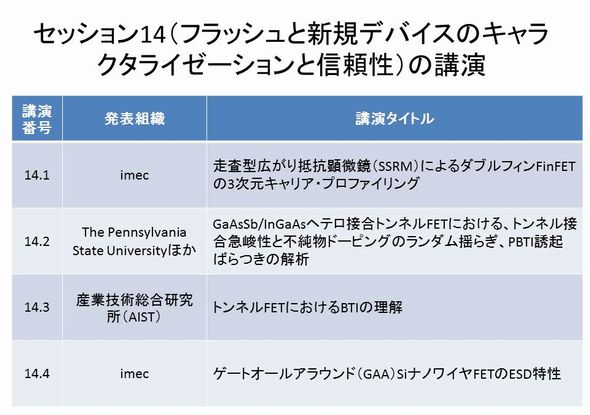

セッション14(キャラクタライゼーション、信頼性、歩留まり)のテーマは、「フラッシュと新規デバイスのキャラクタライゼーションと信頼性」である。最先端デバイスの特性を解析した研究成果の発表が相次ぐ。

ベルギーのimecは、サブ10nmと微細なFinFETのキャリア分布を3次元的に捉える手法を開発した(講演番号14.1)。走査型広がり抵抗顕微鏡(SSRM)を改良した観察手法である。空間分解能は1nmに達する。

米国のThe Pennsylvania State UniversityとUniversity of California, Santa Barbara、IntelとインドIIT Bombayで構成される共同研究チームは、ヘテロ接合トンネルFETの3次元構造を原子オーダーで解析する手法を報告する(講演番号14.2)。GaAs0.4Sb0.6/In0.65 Ga0.35Asヘテロ接合トンネルFETのトンネル接合の急しゅん性と、ソースの不純物濃度分布のランダムばらつきを推定した。分解能は2.4nmである。さらに、HfO2、HfO2-ZrO2、ZrO2といった高誘電体ゲート膜のPBTI特性を評価した。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR