人工知能プロセッサと8K UHDのH.265/HEVCデコーダ:福田昭のデバイス通信 ISSCC 2016プレビュー(4)(1/2 ページ)

今回はセッション12〜14を紹介しよう。セッション14では「次世代のプロセッシング」というテーマに沿って、ディープラーニング専用コアを搭載したプロセッサや、運転者の意図を予測する機能を備えたADAS(先進運転支援システム)向けSoCなど、人工知能プロセッサの発表が相次ぐ。

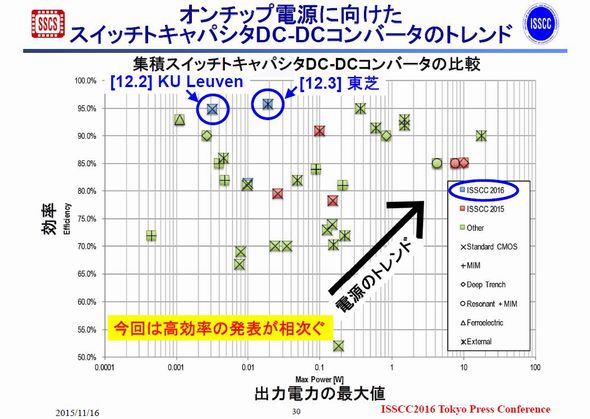

変換効率が高いオンチップDC/DCコンバータ

前回に続き、ISSCC 2016の技術講演セッションから、2016年2月2日(火曜日)午後に発表予定の講演論文のハイライトをお届けしよう。

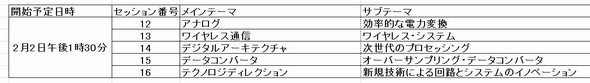

この時間帯は、セッション12からセッション16までの5本のセッションが同時並行に進行する。メインテーマは、セッション12が「アナログ」、セッション13が「ワイヤレス通信」、セッション14が「デジタルアーキテクチャ」、セッション15が「データ・コンバータ」、セッション16が「テクノロジディレクション」である。

それでは、セッション12から順番に、注目講演をご紹介する。セッション12のサブテーマは「効率的な電力変換」である。具体的には、DC/DCコンバータ技術の開発成果が主に披露される。特に目立つのは、高い変換効率を達成した2件のDC/DCコンバータ技術の論文だ。

KU Leuvenは、変換効率が94.6%と高く、標準的なCMOSプロセスでフル集積したスイッチトキャパシタ方式DC/DCコンバータを発表する(講演番号12.2)。オンチップ・キャパシタの寄生容量による効率低下を回路技術の工夫によって軽減している。東芝は、変換効率が95.8%と高いスイッチトキャパシタ方式の昇降圧型DC/DCコンバータを報告する(講演番号12.3)。1入力、2出力で、入力電圧範囲は0.85V〜3.6Vと広い。キャパシタはオンチップとオフチップを併用した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増