16nm「Zynq」は消費電力5W以下、自動運転向け?:カーエレ展でデモ展示(1/2 ページ)

ザイリンクスは、2016年1月13〜15日に東京ビッグサイトで開催された「国際カーエレクトロニクス技術展」で、先進運転支援システム向けのソリューションの展示を行った。

ザイリンクスは、2016年1月13〜15日に東京ビッグサイトで開催された「国際カーエレクトロニクス技術展」で、先進運転支援システム(ADAS:Advanced Driving Assistant System)向けのプログラマブルソリューションのデモ展示を行った。

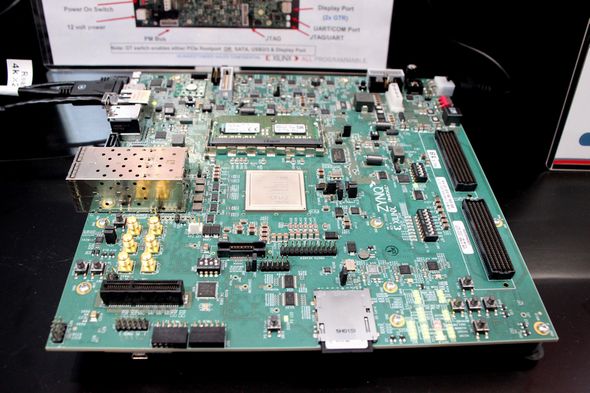

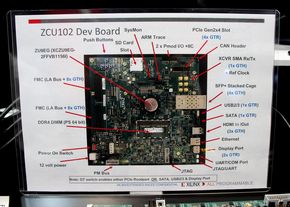

デモが行われたのは、同社が2015年10月からサンプル出荷を開始した16nmプロセスを用いたCPUコア搭載型FPGA「Zynq UltraScale+ MPSoC」と、「Zynq-7000 All Programmable SoC」を活用した歩行者や車両の検出/追跡である。

消費電力は5W以下

最初に紹介するのは、「Zynq UltraScale+ MPSoC」だ。ザイリンクスのマーケティング部でシニアマネージャーを務める神保直弘氏は、「Zynq UltraScale+ MPSoCの1番の強みは、システムに必要な多種のプロセッサが、ハードウェアプログラマブルなFPGAと1チップに搭載されていることである」と語る。

Zynq UltraScale+ MPSoCは、「ARM Cortex-A53」を4コア、「ARM Cortex-R5」を2コア搭載している。GPUとして「ARM Mali-400」も搭載。従来の半導体プロセスはこのような高集積度を難しかったが、TSMCの16FF+(FinFET プラス)プロセスを採用したことにより実現。従来製品と比較して単位ワット当たりの性能を最大5倍に引き上げ、システム全体の高性能化や小型化、低消費電力化、低コスト化を可能にしたという。

展示では、ARM Cortex-A53上で負荷をそれぞれ98〜99%かけた処理の重いシミュレーション、ARM Cortex-R5上ではわざと通信エラーが発生する仕掛けに対して、不具合を検知/回避するシステム制御、ARM Mali-400上では、OpenGL ES2.0での2D/3D処理を行い、4Kディスプレイに表示するデモが行われていた。

同システムは4つのCPUを98〜99%使用していたとしても、各種プロセッサの合計で消費電力が5W以下に収まることが分かった。消費電力5W以下を実現できた理由として、最先端の16FF+プロセス採用と製品設計の工夫を行ったことを挙げる。製品設計は、想定されたADASでのシステム要求仕様を考え、MPSoCが消費する電力をどれくらいに抑えなければいけないかをふまえたという。「従来の製品はADAS向けだったが、Zynq UltraScale+ MPSoCは、自動運転向けに検討する顧客も多い」(同社)とした。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増