高周波圧電共振器の課題を解決する回路:IoT用無線モジュールから水晶が消える!?(2/2 ページ)

サイズも小さく

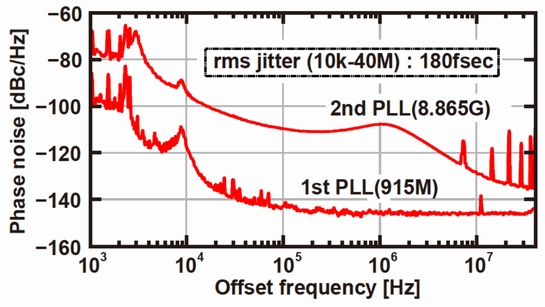

開発したアルゴリズムは、出力信号の位相雑音を抑え、後段PLLのループフィルターの物理的サイズを小さくできるという利点がある。初段PLLのアナログ出力信号f1st(後段PLLの位相参照信号)の位相雑音は、それが圧電共振器を用いた発振器で決まるように設計することで極めて小さくできる。さらに、この参照信号の周波数は高いため、後段PLLのループ帯域を広く設計できる。その結果、後段PLL出力信号の位相雑音の大部分が初段PLLの位相雑音で決まるように設計できるため、最終的な出力信号の位相雑音を小さくできる。参照信号の周波数が高いため、後段PLLのループフィルターの物理的サイズも小さくできるわけだ。

さらに、初段PLLは32kHzの参照信号で低速動作するため、小さい電力で高ビットのデルタシグマ(ΔΣ)変調器が利用できる。開発したPLL回路では、20ビットのΔΣ変調器を使用し、理論上1ppb以下の周波数分解能を実現できる。

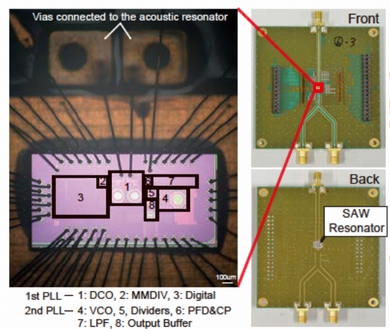

65nm CMOSプロセスで試作

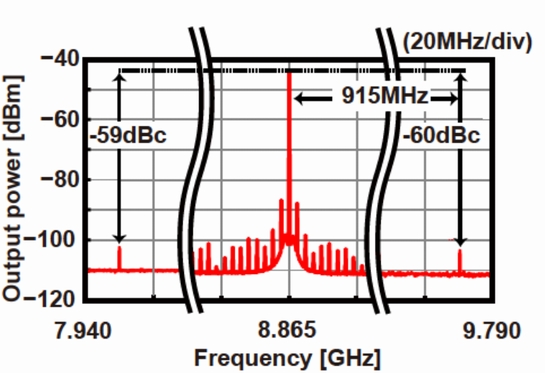

開発したPLLをシリコンウエハーを用いた65nm CMOSプロセスで試作したところ、約9GHzの信号を出力し、180フェムト秒のRMSジッタを12.7mWの消費電力で実現。この性能は、PLLの性能指数(FoM)で−244dBに相当し、小数点分周(フラクショナルN)PLLとして「世界トップクラスの性能」(東工大/NICT)とする。

こうした開発成果を踏まえ、東工大とNICTは「(現状の無線通信システム回路で)外付け部品である水晶発振器を、集積回路に内蔵可能な高周波圧電共振器に置き換えることが可能となり、IoT時代に向けた無線通信システムの小型化・低コスト化・高速化に大きく貢献する」としている。

関連記事

「シリコンは水晶に必ず勝てる」――SiTime

「シリコンは水晶に必ず勝てる」――SiTime

かつては水晶の独壇場だった発振器市場において、MEMSの存在感が高まっている。温度補償機能を備えていない最もシンプルなタイプの発振器では、MEMSの出荷数が既に水晶を上回っている。そのMEMS発振器市場でシェア90%を獲得しているのがSiTimeだ。 “双子の水晶”で高精度化――日本電波のOCXO

“双子の水晶”で高精度化――日本電波のOCXO

日本電波工業は「MWE 2015」で、同社の主力製品であるOCXOなど一連の製品群を展示した。独自の「ツイン水晶振動子」技術を採用したOCXOは、より高精度化、より小型化を図っている。 A-Dコンバータを用いた新方式PLLを開発

A-Dコンバータを用いた新方式PLLを開発

東京工業大学は2015年3月10日、同大学教授の松澤昭氏らの研究グループが、A-Dコンバータを用いた新しい方式のデジタルクロック生成器の開発に成功したと発表した。 “なんとなく”じゃない! ビールのコクが分かるクリスタル

“なんとなく”じゃない! ビールのコクが分かるクリスタル

日本電波工業は、「CEATEC JAPAN 2013」(2013年10月1日〜5日、幕張メッセ)で、サッポロビールと共同で開発している、ビールの味を定量的に評価する味覚センサーシステムを公開した。ピコグラムレベルの微少な重さが計測できる水晶の性質を利用し、ビールに含まれる「コク」につながる味成分の量を測定し、「コク」を数値化する。将来的には、ビールの「キレ」も測定できる見込みの他、さまざまな飲料の味成分を数値化できる可能性があるという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(前編)

- EVに吹く逆風 デンソーの焦りとロームが求める勝機とは

- ヘリウム調達停止――AIブームを崩壊させる「見えない臨界点」(後編)

- 石炭灰から「レアアース元素」を回収、新日本繊維【訂正あり】

- 半導体産業を下支え 台湾スタートアップの「3つの特徴」とは

- 「27年度後半の2nm量産誓う」 Rapidus、解析センター開設

- AIと地政学リスクが招く深刻なメモリ危機

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 経産省、Rapidusに6315億円追加支援 「国益のため必ず成功」

- 26年の半導体市場は64%成長で1.3兆ドルに NAND価格は234%上昇