2020年、5nm世代でEUV時代が到来か:まだまだ光源に開発余地残るが(1/2 ページ)

ASMLは2016年4〜6月にEUV(極端紫外線)リソグラフィ装置を4台受注し、2017年には12台を販売する計画を明かした。これを受けて業界では、EUV装置によるチップ量産が、5nmプロセス世代での製造が見込まれる2020年に「始まるかも」との期待感が広がっている。

ASMLの受注好調&17年12台の販売計画で期待感

ASMLは2016年4〜6月に、EUV(極端紫外線)リソグラフィ装置を4台受注したと発表した。また2017年には、12台のEUV装置を販売する予定だという。

この発表を受け、これまで長期間にわたり遅々として進まなかったEUVスキャナーによる量産体制が、5nmプロセスチップ向けとして2020年にようやく整うことになると期待が高まっている。しかし、この楽観的な新しいスケジュールに対し「13nmと同程度の微細な線幅を印刷するために使われていたシステムを、5nm以降のプロセスで使用するには、重要な光学アップグレードを行う必要があるのではないか」とする懸念も生じている。

ASMLの広報担当者は、「当社の予測では、EUV装置は、10nm台半ばのプロセス世代メモリの2層以上や、最先端の論理ノード(7nmまたは5nm)の6〜9層において使われるようになるとみている」と述べている。

EUVの製造能力、2018年に倍増の「24台/年」に

ASMLは、「2018年には、製造能力を24台に倍増できる見込みだ。1台当たりの価格は、約1億米ドルとなる」としている。現在のところ、8台の最新型EUV装置が半導体メーカーに設置され、試験が行われているという。

Semiconductor AdvisorsのアナリストであるRobert Maire氏は、TSMCが最近、5nmプロセスにおいてEUV装置を使用すると発表したことについて触れながら、「EUV装置の生産が本格化する出発点となるのは、2020年に5nmプロセスでの使用が開始する時だ」と述べている。

また同氏は、「Intelは2016年7月20日に、同年秋には10nmプロセスの量産を開始する予定であることを明らかにした。同社の10nmプロセス開発はこれまで、遅れが生じているとみられていたが、それが否定されることになった。Intelは、7nmプロセスにおいてEUV装置を使用し、TSMCの5nmプロセスとほぼ同時期に量産を加速させることになるだろう」と述べる。

現在、16nmおよび14nmプロセス世代では一般的に、既存のDUV(深紫外線)スキャナーでダブルパターニングを使用することにより、極めて微細なラインとスペースを実現することが可能だ。10nm以降のプロセスにおいてEUV装置を利用できるようになれば、高コストで難度も高いトリプルパターニングないしクアッドパターニングを使用する必要がなくなるかもしれない。

10nm世代の寿命短く、7nm世代が重宝される?

半導体メーカーは、20nmプロセスにおいてダブルパターニングを使うようになって以来、プロセス名の扱いが雑になったのではないだろうか。Maire氏は、最新のニュースレターの中で、GLOBALFOUNDRIESのチーフテクノロジストが2016年初めに語っていた見解に賛同しながら、「10nmプロセスの寿命は、業界全体が7nmプロセスを強力に推進し始めるころまでしか続かず、“ライトノード”(Lite' node)になるのではないか。一方、7nmプロセスは、強力で長く続くとみられている」と述べている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

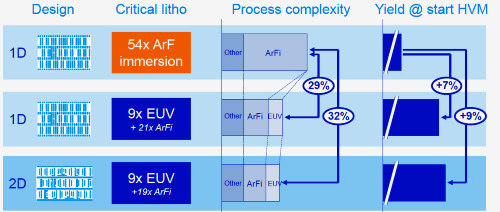

ASMLは、「EUVを使用すれば、マルチパターニングが不要になり、歩留まりも改善する」と主張する 出典:ASML

ASMLは、「EUVを使用すれば、マルチパターニングが不要になり、歩留まりも改善する」と主張する 出典:ASML