NVIDIAがエネルギー効率の高い相互接続技術を解説(後編):福田昭のデバイス通信(100) 高性能コンピューティングの相互接続技術(5)(1/2 ページ)

相互接続(インターコネクト)に電荷再利用型バス(Charge Recycling Bus)を利用すると、エネルギー効率を高めることができる。だが、電荷再利用型バスにも弱点は存在する。今回は、電荷再利用型バスの課題とそれを解決する技術を紹介しよう。

電荷再利用型バス技術の問題点

2016年12月に開催された国際学会IEDMのショートコースから、「将来のコンピュータにおける相互接続の課題(Interconnect Challenges for Future Computing)」と題するNVIDIAの講演概要をご紹介している。講演者はNVIDIAで研究担当シニア・バイスプレジデント兼チーフサイエンティストを務めるWilliam(Bill) Dally氏である。

シリーズの第4回である前回は、エネルギー効率の高い相互接続技術を一部、説明した。今回は、その後編である。

なお講演だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、Dally氏の講演内容を適宜、補足している。あらかじめご了承されたい。

本シリーズの初回で説明したように、先端SoC(System on a Chip)では演算器やメモリなどのトランジスタ回路よりも、バスやリンクなどの相互接続(インターコネクト)が大きなエネルギーを消費する。

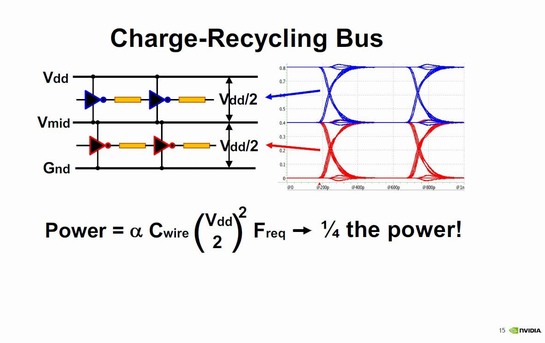

前回の後半では、電荷再利用型バス(Charge Recycling Bus)技術をご紹介した。バスを複数の並列なバスに分割し、上下のバスで電荷を融通することで消費電力を下げる技術である。なお講演では触れられなかったようだが、電荷再利用型バス技術は、1994年に日本の松下電器産業(当時)の技術者である山内寛行氏らが開発した(国際学会VLSI Circuitsで1994年6月に発表された)。

電荷再利用型バスの弱点は、中間電位をどのようにして電源電圧と接地電圧の中央に維持するかにある。上下のバスでスイッチング電流にアンバランスがあると、中間電位がずれて雑音となってしまう。

解決策の1つに、電圧レギュレーターの挿入がある。しかし電圧レギュレーターの挿入によるシリコン面積の増加と消費電力の増加はかなり大きく、本来の目的である「相互接続の消費電力低減」を損なう恐れが少なくない。

そこでDally氏らの研究グループが開発したのが、「BCRB(Balanced Charge Recycling Bus:バランス型電荷再利用バス)」と呼ぶ改良版の電荷再利用型バス技術である。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング