EE Times Japan >

部品/材料 >

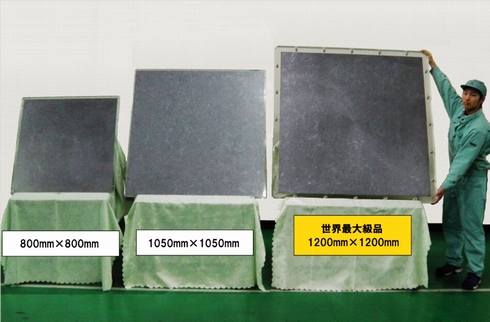

一辺1200mm超える柱状晶シリコン製造技術を確立:2016年度中にサンプル出荷へ

三菱マテリアルは2017年1月、一辺が1200mmを超える「世界最大級」の柱状晶シリコン製造技術を確立したと発表した。2016年度中をめどに、サンプル出荷を開始する予定である。

» 2017年01月27日 10時30分 公開

[庄司智昭,EE Times Japan]

精密鋳造技術を駆使

三菱マテリアルの電子材料事業カンパニーは2017年1月、三菱マテリアル電子化成と共同で、一辺が1200mmを超える柱状晶シリコンの製造技術を確立したと発表した。

柱状晶シリコンは、一方向に結晶を成長させて凝固させた「柱状」の結晶構造を持つ多結晶シリコンである。シリコンは材料が脆性(ぜいせい)であることに加え、凝固過程において膨張するため、大型になると割れやすいといった特徴がある。

同社は、長年培った精密鋳造(ちゅうぞう)に関するノウハウを生かし、高純度化と内部応力の低減を実現する製造技術を確立。実用性の高い「世界最大級」の大型柱状晶シリコンを、安定的に製造することに成功したという。

同技術の確立により、現在柱状晶シリコンが利用されている半導体製造装置用部材(プラズマエッチング装置用、均熱版など)やスパッタリングターゲット材料などの利用拡大が見込む。半導体装置において他の素材を利用していた大型部材やフラットパネルディスプレイなど、さまざまな製品分野での利用拡大も期待できるとした。

2016年度中をめどに、大型柱状晶シリコンのサンプルを出荷予定。2017年2月15〜17日に東京ビッグサイトで開催される「新機能性材料展2017」にも展示予定である。

関連記事

ISS 2017で語られた半導体技術の今後(前編)

ISS 2017で語られた半導体技術の今後(前編)

米国で開催された「Industry Strategy Symposium(ISS)」(2017年1月8〜11日)では、半導体技術の今後に関する議論が幾つか展開された。ナノワイヤトランジスタやGAA(Gate All Around)トランジスタといった次世代トランジスタ技術や、増加の一途をたどる設計コストなどについて、専門家たちが見解を披露している。 ムーアの法則の“新たな意味”とは

ムーアの法則の“新たな意味”とは

台湾半導体産業協会の専門家は、今後ムーアの法則は、「半導体の集積率の向上」というよりも、より実質的な意味を持つようになると指摘する。3次元構造やTSMCの「InFO」のようなパッケージング技術によって性能の向上を図っていくというものである。 450mmウエハーへの移行、業界は消極的

450mmウエハーへの移行、業界は消極的

SEMIが米国で開催した「Industry Strategy Symposium(ISS)」(2017年1月8〜11日)では、450mmウエハーの話題はほとんどなかった。450mmウエハーへの移行に積極的だった半導体業界だが、ここ最近はそうでもないようだ。 銅コアの部品内蔵基板が“小型化”にもたらす可能性

銅コアの部品内蔵基板が“小型化”にもたらす可能性

太陽誘電は「第46回 インターネプコン ジャパン」(2017年1月18〜20日/東京ビッグサイト)で、モジュールの小型化に貢献する部品内蔵配線基板「EOMIN」などを展示した。 解像度2μmを実現、FOPLP向け直接描画露光装置

解像度2μmを実現、FOPLP向け直接描画露光装置

SCREENセミコンダクターソリューションズは、半導体後工程のFOPLP(Fan-Out Panel Level Package)向けに、解像度2μmを実現した直接描画露光装置「DW-3000 for PLP」を開発、2017年1月より販売を始める。 次世代Snapdragon、Samsungの10nmプロセスを適用

次世代Snapdragon、Samsungの10nmプロセスを適用

Qualcommは、同社のSoC(System on Chip)「Snapdragon 835」に、Samsung Electronicsの10nmプロセスを適用すると発表した。QualcommはSamsungとの間で、ファウンドリー契約を10年延長している。

Copyright © ITmedia, Inc. All Rights Reserved.

Special ContentsPR

特別協賛PR

スポンサーからのお知らせPR

Special ContentsPR

Pickup ContentsPR

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Special SitePR

あなたにおすすめの記事PR