16nm MPSoCにRFデータコンバーターを統合:5Gワイヤレスを視野に(1/2 ページ)

Xilinx(ザイリンクス)は、RFクラスのアナログ技術を統合した「All Programmable RFSoC」について、その技術概要を発表した。

消費電力とフットプリント、従来比50〜75%削減

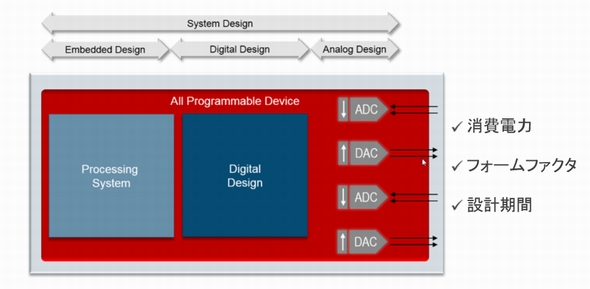

Xilinx(ザイリンクス)は2017年2月、RFクラスのアナログ技術を統合した「All Programmable RFSoC」の要素技術について、その概要を発表した。5G Massive MIMO無線システムやミリ波無線バックホールにおいて、消費電力とフットプリントを従来に比べて50〜75%も削減できるという。

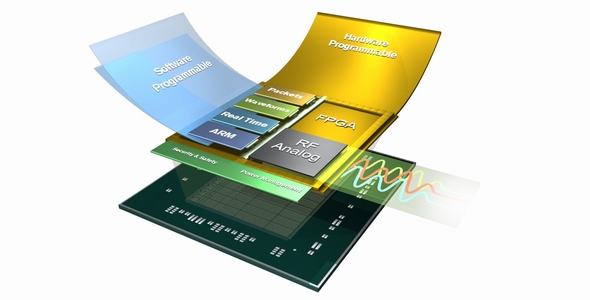

All Programmable RFSoCは、TSMCの16nm FinFETプロセスを用いた「All Programmable MPSoC」をベースとしている。これに、サンプリングレートが最大4Gサンプル/秒で分解能が12ビットのA-Dコンバーターや、同じく最大6.4Gサンプル/秒で14ビットのD-Aコンバーターなど、ダイレクトRFサンプリングを可能とするRFアナログ回路ブロックを新たに集積した。新たなプロセス技術は追加していないという。

All Programmable RFSoCを用いると、入力/出力RF信号をダイレクトにサンプリングできるため、従来のIF(中間周波数)サンプリングシステムで用いていたミキサーやオシレーターといったアナログ部品を削減することができる。

また、ダイレクトRFサンプリング回路はこれまで、データコンバーターとDSPベースのミキサー&フィルターで構成されているのが一般的だ。このデバイス間の信号伝送には、JESD204B/Cプロトコルに基づく高速シリアルインタフェースが採用されている。このため、インタフェース部の設計負荷や電力消費の増大などが課題となっていた。

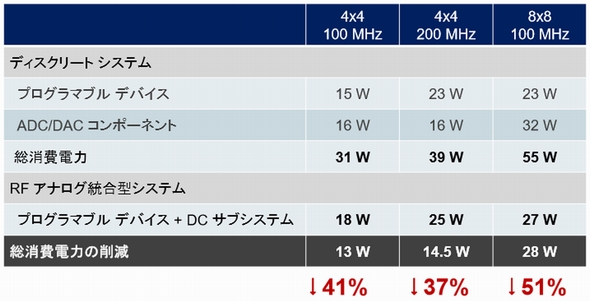

これらの課題に対してAll Programmable RFSoCは、データコンバーターをワンチップに集積したことで、JESD204B IPコアとシリアルトランシーバーが不要となり、設計の期間短縮を可能とした。消費電力も大きく削減することができるという。標準的な受信4本、送信4本のアンテナ構成だと、データコンバーターを外部に接続した場合に比べて電力消費は約40%も削減することができる。8×8のシステムだと従来システムで55Wとなる。これに対してRFSoCを用いると27Wで済み、半分以下に削減することが可能だという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

RFアナログ技術を統合したAll Programmable RFSoCの回路ブロックイメージ 出典:ザイリンクス

RFアナログ技術を統合したAll Programmable RFSoCの回路ブロックイメージ 出典:ザイリンクス