近接場結合を用いた3D集積、電力効率の1桁改善を:慶応大の黒田忠広氏が語る(1/2 ページ)

電力効率の改善なくして、性能改善なし。 慶応義塾大学の理工学部電子工学科で教授を務める黒田忠広氏は、講演内でこう語る。電力効率の改善には新しいトランジスタ構造などの導入が検討されているが、黒田氏が提案するのは「近接場結合」による3D集積技術である。

「電力効率改善なくして、性能改善なし」

ムーアの法則が死んだといわれているが、果たして本当に死んだのだろうか――。

芝浦工業大学グリーンイノベーション研究センターが、2017年2月に開催した「第4回グリーンイノベーションシンポジウム」で、慶應義塾大学の理工学部電子工学科で教授を務める黒田忠広氏は、講演冒頭でこう語った。

この問いの答えは人によってさまざまだが、黒田氏は「重要な問いは“いつ”終わるのかではなく、“なぜ”終わるのかという議論」と語る。

ムーアの法則は、性能コスト比を改善できなくなったときに終わる。コストはリソグラフィ技術で決まり、性能は電力効率で決まる。リソグラフィ技術に関しては限界に近づくと、トランジスタの単価は上がる。事実16nmからトランジスタの単価が上昇しているが、EUV(極端紫外線)の導入で解決することが期待されている。

つまり、黒田氏は「本質的な問題は、電力が上限に達して集積を妨げること」であり、「電力効率(=処理性能/電力)の改善なくして、性能改善なし」と強調した。

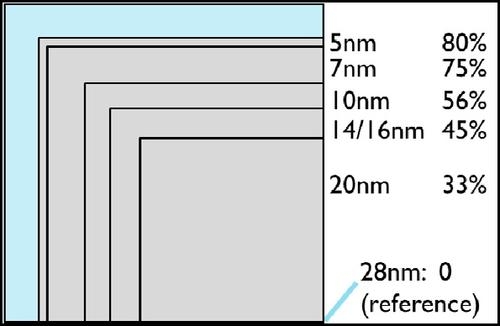

電力効率が重要なのは、電力が上限に達してしまい集積しても電源を投入できないトランジスタ「ダークシリコン」の問題からも分かる。28nmプロセスでは、ダークシリコンの比率はゼロだが、集積化が進むほどその比率は増加するといわれている。20nmでは33%、16nmで45%、10nmで56%、7nmで75%、5nmになると80%という。

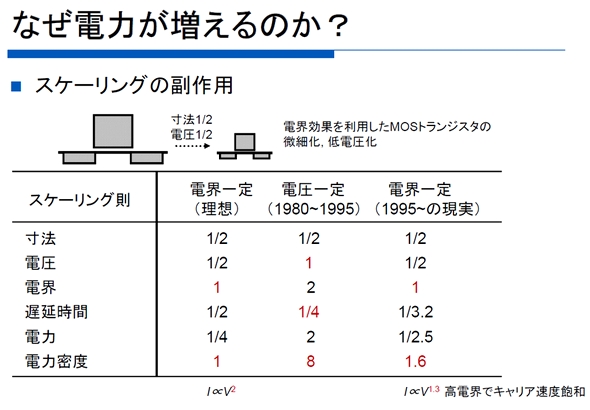

電力が増加する要因は、スケーリングの副作用によるものだ。1980〜1990年代にかけて、電圧一定のスケーリングで動作速度を優先した結果、デバイス内部の電界は非常に高くなった。1995年以降は電界一定のスケーリングに切り替えたが、高電界でキャリアが速度飽和し、電圧を下げたとしても電力が効果的に減らなかったという。

低電力化に向けた3つの方策

黒田氏は、低電力化への方策として1)低電圧化、2)低容量化、3)低活性化を挙げた。低活性化は、スイッチングの回数を減らすために、効率の高いアルゴリズムを見いだすことが必要なため、現実的ではない。低電圧化と低容量化に期待が掛かるとする。

低電圧化に向けて立ちはだかるのは、リーク電流だ。黒田氏は「トランジスタが微細になればなるほど、ゲートの支配力が低下するため、リーク電流が増加する。全体の電力における約20%がリーク電流になる電源電圧よりも下げてしまうと、消費電力は全体としてかえって増えてしまうことが研究から分かっている」と語る*)。

*)メモリやプロセッサなど回路の構成で、電圧の下限は異なるという。

リーク電流を減少させる方法として考えられている有効な方法は、トランジスタの構造を変えることである。これまでにもUltra Thin BodyやFinFET、ナノワイヤによる新しい構造が検討されてきた。トンネルFET(T-FET)も期待されているが、トンネル現象を利用するためオン電流が小さく、FinFETに比べて実用化が難しいのが現状という。

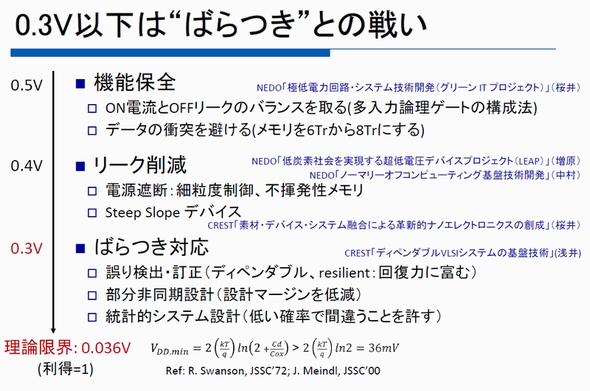

「現在、電源電圧0.3Vに向けて研究が進んでいる。0.3V以下になると、素子のばらつきが多くなるため、誤り検出、誤り訂正といった“回復力に富む機能”が求められるなど、設計が困難だ。理論的に電源電圧の限界値は、0.036Vである。そのため低電圧化による電力低減の余地は、あと2桁(E=CV2のため)残っていることになる」(黒田氏)

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 次世代パワー半導体 「期待の5材料」の現在地

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「3社のパワー半導体事業を切り出し合弁設立したい」三菱電機社長

- パワー停滞も光デバイス堅調、三菱電機の半導体部門

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

黒田忠広氏

黒田忠広氏 プロセスノードごとのダークシリコンの割合 出典:ARM

プロセスノードごとのダークシリコンの割合 出典:ARM