Cypress、低消費でより強固なセキュリティ実現:IoT機器に特化した新PSoC(1/2 ページ)

Cypress Semiconductor(サイプレス セミコンダクタ)は、IoT機器に向けたマイクロコントローラ(MCU)アーキテクチャ「PSoC 6」を発表した。デュアルCPUコア構成とし処理性能を向上しつつ、消費電力を抑えた。セキュリティ機能もハードウェアベースで実装した。

デュアルCPUコア構成、HWでセキュリティ機能を内蔵

Cypress Semiconductor(サイプレス セミコンダクタ)は2017年3月13日、IoT機器に向けたマイクロコントローラ(MCU)アーキテクチャ「PSoC 6」を発表した。デュアルCPUコアの構成とすることで、処理性能を向上しつつ消費電力を抑えた。セキュリティ機能もハードウェアベースで実装している。

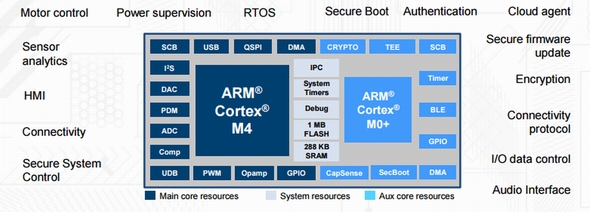

PSoC(プログラマブルSoC)は、CPUコアやメモリの他、ユーザーモジュールと呼ばれるアナログやデジタルブロックを集積している。静電容量センシング技術「CapSense」などを搭載しているもの特長の1つだ。

新たに発表した「PSoC 6」は、これらの特長を継承しながら、IoT機器で求められる機能/性能を新たに盛り込んだ。その1つがデュアルコアアーキテクチャの採用である。「ARM Cortex-M4」および「Cortex-M0+」と、2種類のCPUコアを内蔵している。

システムコントロールなど比較的高い演算能力を求められる処理をCortex-M4が主に担当し、スタンバイモード時の処理や通信制御などをCortex-M0+で実行することができる。処理負荷に応じて演算を分担することにより、MCUとしての処理性能と消費電力の最適化を実現した。プロセス技術はこれまで用いてきた130nm技術ではなく、独自のウルトラローパワー40nmSONOS技術を新たに採用した。

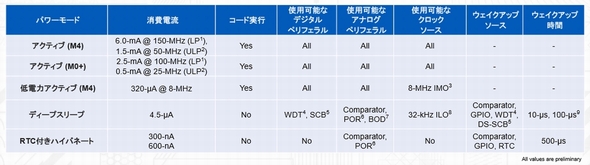

新開発のプロセス技術を用いることで、極めて小さいアクティブ電力を実現した。Cortex-M4コアで22μA/MHz、Cortex-M0+コアは15μA/MHzである。また、動的電圧周波数スケジューリング(DVFS:Dynamic Voltage and Frequency Scaling)機能を搭載した。ローパワー(LP)モード時の動作電圧は1.1V、ウルトラローパワー(ULP)モード時の動作電圧は0.9Vとなる。

この結果、Cortex-M4コアの場合、LPモードで150MHz動作時の消費電流は6.0mAとなる。ULPモードで50MHz動作時は1.5mAである。同様にCortex-M0+コアだと、LPモードで100MHz動作時に消費電流は2.5mA、ULPモードで25MHz動作時の消費電流はわずか0.5mAと小さい。これ以外にも、クロックを8MHzに下げる低電力アクティブモードや、CPUコアの動作を停止し周辺ブロックのみ動作状態となるディープスリープモードなどを用意している。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増