Intelが10nmプロセスの詳細を明らかに:競合に対する優位性を示す?(1/2 ページ)

Intelは2017年に10nmチップ製造を開始する予定だ。さらに、22nmの低電力FinFET(FinFET low power、以下22nm FFL)プロセスも発表した。GLOBALFOUNDRIESなどが手掛けるFD-SOI(完全空乏型シリコン・オン・インシュレーター)に真っ向から挑み、ファウンドリービジネスで競い合う。

この記事は会員限定です。会員登録すると全てご覧いただけます。

22nmの低消費電力FinFETプロセス

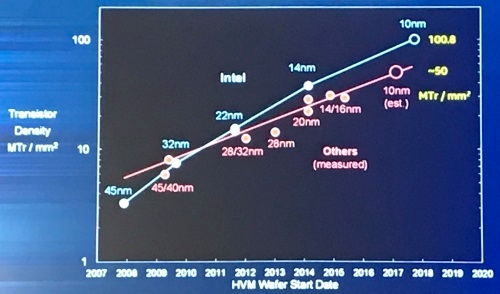

Intelは10nmプロセスで、1mm2当たり1億80万個のトランジスタを詰め込む計画である。既にリスク量産が始まっているTSMCやSamsung Electronicsの10nmプロセスのトランジスタ密度はその約半分だという。

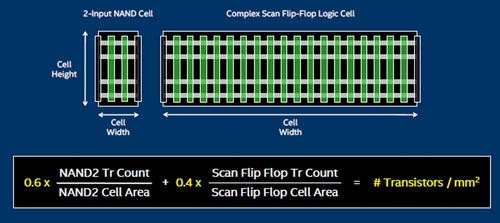

トランジスタ密度を計算するIntelの指標は、小型および大規模なロジックセルの密度を平均化したものである。具体的には、同社は2個のアクティブゲートを備えた2入力のNANDセルと、25個のアクティブゲートを備えたスキャンフリップフロップセルを用いている。

Intelのシニアフェローで、プロセスアーキテクチャおよび統合部門のディレクターを務めるMark Bohr氏は「当社の指標は包括的かつ定量的である上に公正さも備えている」と述べた。

現在のプロセスノードは、実際の長さというよりは「ノード間の相対的な進歩」を示しているようなものだ。

指標がどのようなものでも、Intelは14nmプロセスに移行してから3年目となる2017年後半に、10nmプロセスを適用する次世代プロセッサ「Canon Lake」の製造を開始する計画だ。同社は次のノードに3年で移行するというペースを維持することを望んでいるが、10nmプロセスでは1年目と2年目にもアップグレードを予定している。同プロセスは1年目のアップグレード後は「10+」、2年目は「10++」と呼ばれるようになるという。

ただ、実は、初期の10nmプロセスよりもIntelの「14++」プロセスの方が高い性能を備えている。とはいえ、10nmプロセスは、より低い消費電力と、より高いトランジスタ密度を実現している。

Intelは10nmノードについて、いつもよりも詳細を明らかにしている。ファウンドリービジネスで競合するTSMCとSamsungが既に10nmプロセスを始動させていることから、Intelは、同プロセスにおける優位性をより積極的に示す必要があったのだろう。

Intelの10nmプロセスは、フィンピッチが34nm、フィンの高さが53nm、メタルピッチは最小で36nm、セル高さは272nm、ゲートピッチは54nmとなっている。

アナリストらはIntelの10nmプロセスに感銘を受けたようだが、競合に対する優位性があると判断する基準としてトランジスタ密度が最適なのかどうかについては、意見が分かれた。プロセスが28nmから16nmや14nmに進むにつれて、競争は激しさを増すばかりである。そうした状況の中で、どこがけん引するのかについては、現段階ではまだ何ともいえないようだ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- 最新ノートPC5機種を分解 新旧MacBook Proの中身の違いは?

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- 「装置は動くがプロセスが成立しない」――He供給危機とナフサ不足の本質

- 次世代パワー半導体 「期待の5材料」の現在地

- He/ナフサ供給危機で工場新設も遅延? 装置/チップメーカーへの波及経路を探る

- Apple新CEOはエンジニア出身 製品開発重視への回帰か

- ルネサス26年1Qは増収増益 車載/AI好調で「足元は当面強い」

Intelは、同社の10nmプロセスにおけるトランジスタ密度は、競合の2倍になると主張する

Intelは、同社の10nmプロセスにおけるトランジスタ密度は、競合の2倍になると主張する