埋め込みフラッシュIP大手ベンダーSSTのメモリ技術:福田昭のストレージ通信(95) STが語る車載用埋め込み不揮発性メモリ(8)(1/2 ページ)

今回は、SST(Silicon Storage Technology)が開発した埋め込みフラッシュメモリ技術を紹介する。同社は「SuperFlash(スーパーフラッシュ)」と呼んでいるが、その最大の特徴はスプリットゲート方式にある。

スプリットゲートの埋め込みフラッシュを開発したSST

国際会議「IEDM」の「ショートコース(Short Course)」から、車載用の埋め込み不揮発性メモリに関する講座「Embedded Non Volatile Memories for Automotive Applications」の概要をご紹介している。講演者は半導体ベンダーSTMicroelectronics(STマイクロエレクトロニクス)のAlfonso Maurelli氏である。

なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

前回は、講演者の所属企業である、STMicroelectronicsの埋め込みフラッシュメモリ技術に関する講演部分をご紹介した。今回は、埋め込みフラッシュIPの大手ベンダーであるSST(Silicon Storage Technology, Inc.)のメモリ技術を説明していく。

SSTの埋め込みフラッシュメモリ技術は、過去にはフラッシュメモリ内蔵マイコン(マイクロコントローラー)の大半に採用されていた。現在も、SSTの埋め込みフラッシュ技術をライセンス導入して自社のマイコン製品に搭載しているマイコンベンダーは、少なくない。

SSTが開発した埋め込みフラッシュメモリ技術(「SuperFlash(スーパーフラッシュ)」と同社は呼んでいる)の最大の特徴は、スプリットゲート方式にある。既に説明したようにスプリットゲート方式は、ゲートを横方向(シリコン表面と平行な方向)に分割することよって制御性を高めたフラッシュメモリ技術だ。メモリセル面積はやや大きめになるものの、アクセス時間が短い、プログラム(書き込み)の消費電流が低い、メモリアクセスのページサイズが小さいといった特長を備える。

スプリットゲート方式の基本的な考え方は、セルトランジスタのゲート電極を、ワード線に相当するゲート電極(「選択ゲート」とも呼ぶ)と、浮遊ゲートに相当するゲート電極の2つで構成することだ。ワード線に低めの電圧を印加することでセルトランジスタがオンになるか、オフのままでいるかによってデータを読み出す。

浮遊ゲートに電荷を蓄積することによってセルトランジスタのしきい電圧を変更する(蓄積するデータの値を変える)点では、スプリット方式は1トランジスタNOR方式と変わらない。違うのは、プログラム(書き込み)の原理である。

SSTが開発したスプリットゲート方式では、プログラム(書き込み)に「SSI(Source Side Injection)」と呼ぶホットエレクトロン注入技術を使う。SSIとはセルトランジスタのソース側に高電界を加えることによってホットエレクトロンの注入効率を高める技術で、1トランジスタNOR方式の書き込み原理であるチャンネルホットエレクトロン(ドレイン電極に高電圧を加える方式)に比べると少ない電流でデータを書き込める。また、CMOSロジックとプロセスの互換性が取りやすいという長所もある。

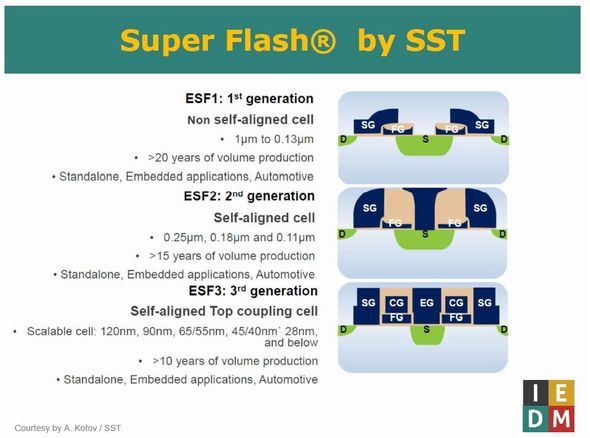

「SuperFlash」技術の歴史はかなり長い。現時点では、第1世代から第3世代までの技術(ESF1〜ESF3)が存在する。SSTの公式資料によると第1世代の量産開始が1994年なので、24年近い量産実績があることになる。

もう少し詳しく説明すると、第1世代の「ESF1」は1μmから0.13μm(130nm)までの製造技術で使われた。ESF1は2つのゲート電極を両方ともリソグラフィで加工していたため、微細化にあまり適していない。そこで第2世代の「ESF2」では、自己整合(セルフアライン)技術を導入してさらなる微細化を可能にした。ESF2は0.25μm、0.18μm、0.11μm(110nm)の製造技術で使われた。15年を超える量産実績を有する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増