FLOSFIA、「成膜」で高品質セラミックスを合成:サーミスターを半導体工程で作る

京都大学発のベンチャー企業であるFLOSFIA(フロスフィア)は、独自の成膜技術「ミストドライ法」を用いて、高品質のセラミックスを合成することに成功した。

高配向性で、表面凹凸が極めて小さい

京都大学発のベンチャー企業であるFLOSFIA(フロスフィア)は2019年1月、独自の成膜技術「ミストドライ法」を用いて、高品質のセラミックスを合成することに成功したと発表した。この技術を用い、小型で面実装タイプのサーミスター素子を試作した。

ミストドライ法とは、霧状にした原材料溶液と加熱部を用いて、酸化物薄膜を化学反応で作製する技術である。京都大学の藤田静雄教授らの研究グループが開発した「ミストCVD法」をベースに、FLOSFIAが「高配向性」で「高純度」「量産可能」な成膜技術に進化させた。

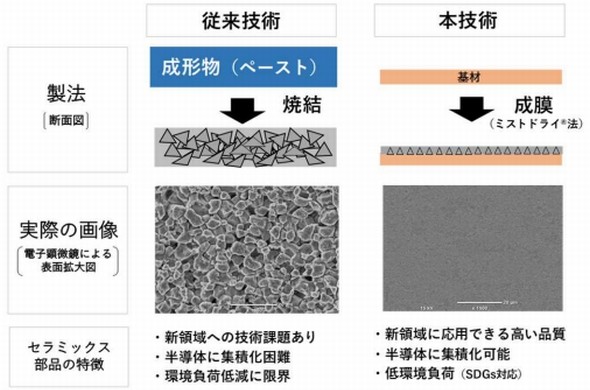

セラミックス部品の製造には、ペースト状の材料を焼き固める「焼結法」を用いるのが一般的だが、通常は1000℃を超える高温での活性化処理が必要になるなど、課題もあった。これに対してミストドライ法は、全ての工程を300〜800℃の温度に抑えることができる。この方法だと、一般的な半導体デバイスとセラミック部品の機能を1チップに集積することも可能になる。

FLOSFIAは既に、ミストドライ法を用いて、オン抵抗が極めて小さいショットキーバリアダイオードを開発している。今回は、この手法をセラミックス作製に適用した。この技術を用い、高配向膜で粒界が極めて少なく、表面凹凸や孔のない高品質のセラミックス薄膜を作製することに成功した。

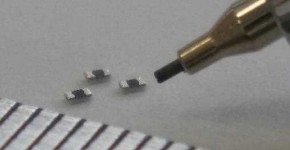

同社は、ミストドライ法を用いてサーミスター素子を試作し、1×0.5mmの面実装パッケージに収めた。原子層レベルでセラミックスを順次、化学合成をすることができるため、薄膜化による低抵抗化、大電流化、センシング温度の感度向上、高周波特性の改善などにつながる可能性が高い。具体的には、抵抗値1Ω以下、周波数10GHz以上での安定動作などが期待できるという。

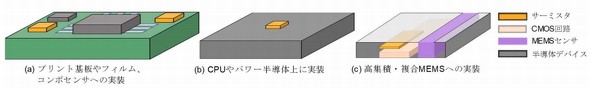

しかも、サーミスター素子は半導体製造プロセスを活用できるため、ロール状のフィルムへの形成、パワー半導体や光デバイス、ロジックICとの1チップ化など、さまざまな実装形態が可能となる。

FLOSFIAは今後、既存のデバイスメーカーやセラミックス部品メーカーと連携し、早期事業化を目指す考えだ。まずはセラミックス部品シリーズとしてサーミスター素子を製品化する。さらに、ウエハーやフィルムでの提供も含め、さまざまな電子デバイスや複合デバイスへの応用を目指す。早ければ2019年下期にもサンプル出荷を始め、2020年には量産に入る予定。2030年には売上高120億円を計画している。

関連記事

デンソーとFLOSFIA、酸化ガリウムパワー半導体の開発で協業

デンソーとFLOSFIA、酸化ガリウムパワー半導体の開発で協業

デンソーとFLOSFIAは、酸化ガリウムパワー半導体の開発で協業すると発表した。車載応用に向け開発を進める。 FLOSFIA、MOSFETのノーマリーオフ動作を実証

FLOSFIA、MOSFETのノーマリーオフ動作を実証

京都大学発のベンチャー企業が、コランダム構造の酸化ガリウムを用いて、ノーマリーオフ型MOSFET(絶縁効果型トランジスター)の動作実証に成功した。 量産間近、酸化ガリウムパワーデバイス

量産間近、酸化ガリウムパワーデバイス

FLOSFIAは「CEATEC JAPAN 2017」で、酸化ガリウムSBD(ショットキーバリアダイオード)を展示している。2018年に、まずは月産30万個の規模で量産を始める予定だ。 基材や形状を選ばない非真空ドライめっき技術

基材や形状を選ばない非真空ドライめっき技術

ベンチャー企業のFLOSFIAは、京都大学が開発した薄膜形成技術「ミストCVD法」を発展させ、基材の種類や形状に関係なく金属薄膜を成膜できる非真空ドライめっき技術「ミストドライ めっき法」を開発した。10μm以下の表面形状にも成膜可能で、半導体素子などの電極への応用が見込まれる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- デンソー、ロームに対する株式取得提案を正式表明

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

従来技術と今回の技術との違い 出典:FLOSFIA

従来技術と今回の技術との違い 出典:FLOSFIA 試作したサーミスター(協力=早木電機) 出典:FLOSFIA

試作したサーミスター(協力=早木電機) 出典:FLOSFIA