最先端プロセスでも歴然の差! チップ面積は半導体メーカーの実力を映す鏡:この10年で起こったこと、次の10年で起こること(37)(3/3 ページ)

先端プロセスでは差が付きにくいとされるが……

現在のチップ設計は基本的に自動設計ツールを使う。プロセステクノロジーはTSMCやSamsungらのファウンドリーの製造ルールに完全準拠する。そのため、「チップの出来栄えに大きな差は現れにくい」と言われている。しかし、実際には図3のように「同一プロセス世代でも2割も3割もチップ面積に差が生まれている!!」わけだ。チップを開封しない限り明らかにならないことである。

どちらが優れているか、という点ではほぼ同等の機能を積んでいるので、甲乙はつけがたい。しかし半導体という点だけで見れば、小さい方がコストは安く、さらに歩留まりも良い。さらに小さいチップは内部の配線距離も短くなるので配線容量も小さくなり、信号の損失も確実に削減されることからも、消費電力が小さい場合が多い。また動作周波数も上げやすい(配線距離に依存するケースが多いため)

このように同等プロセス、同等機能製品ながら2〜3割もの面積差があるという事例はマイコンなどにも多々ある。

やはりチップを開封して各メーカーの設計インプリメント(インプリ)力を常時掌握しておく必要があるのではないだろうか(各社のインプリ力を明確にするためにも)。プロセスや仕様が同じようなものになりつつある現在、インプリ力の差は半導体メーカーに力の差としてもっとも見えやすいところだからである。

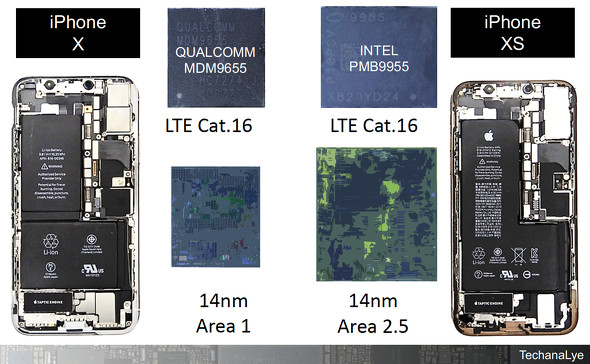

図4は、2017年発売のApple「iPhone X」(左)と2018年モデル「iPhone XS」(右)のLTEモデムチップの様子だ。

左はQualcomm製の14nm 世代モデムチップでLTE Cat.16対応。右はIntelの14nm世代モデムチップで LTE Cat.16対応。同じ世代のプロセスを用い、同じCat.16を実現する。IntelのチップはGNSS機能も備えるものの、チップ面積は実にIntelの方が2.5倍も大きい。

GNSS分を差し引いても、ほぼ2倍のサイズだ。半導体は「誰が作っても同じ」では決してない。メーカーによって今なお、倍半分の差がある世界だ。これがビジネス全体に及ぼす影響は絶大だ。小さいものは取得数が多いからだ。コストに直結する。

依然としてメーカー間の差は大きい。

半導体デバイスはシリコンを見て判断することが、今後もますます重要になる。

筆者Profile

清水洋治(しみず ひろはる)/技術コンサルタント

ルネサス エレクトロニクスや米国のスタートアップなど半導体メーカーにて2015年まで30年間にわたって半導体開発やマーケット活動に従事した。さまざまな応用の中で求められる半導体について、豊富な知見と経験を持っている。現在は、半導体、基板および、それらを搭載する電気製品、工業製品、装置類などの調査・解析、修復・再生などを手掛けるテカナリエの代表取締役兼上席アナリスト。テカナリエは設計コンサルタントや人材育成なども行っている。

関連記事

Galaxy S10 5Gを分解 ―― ケータイで流行した2層基板が再び登場した背景と今後

Galaxy S10 5Gを分解 ―― ケータイで流行した2層基板が再び登場した背景と今後

今回は、Samsung Electronicsの第5世代移動通信(5G)対応スマートフォン「Galaxy S10 5G」の内部などを紹介しながら、最近のハイエンドスマートフォンで主流になっている“基板の2階建て構造”(2層基板)を取り上げる。 iPhone XRとiPad Proの中身に透かし見る最新半導体トレンド

iPhone XRとiPad Proの中身に透かし見る最新半導体トレンド

今回は2018年10〜11月に発売されたAppleの2つの新製品「iPhone XR」と「iPad Pro」の中身を詳しく見ていこう。2機種の他、9月発売の「iPhone XS/同XS Max」とも比較しながら、最新の半導体トレンドを探っていこう。 「XPERIA XZ2 Premium」にみる、スマートフォンの主戦場“カメラ周り”最新動向

「XPERIA XZ2 Premium」にみる、スマートフォンの主戦場“カメラ周り”最新動向

2基のカメラを搭載する「デュアルカメラ・スマートフォン」が当たり前になりつつある。今回は、ソニーとして初めてデュアルカメラを搭載したスマートフォン「XPERIA XZ2 Premium」の内部を観察していく。 わずか0.1mm単位の攻防が生んだiPhone X

わずか0.1mm単位の攻防が生んだiPhone X

Appleが、「iPhone」誕生10周年を記念して発売した「iPhone X」。分解すると、半導体技術のすさまじい進化と、わずか0.1mmオーダーで設計の“せめぎ合い”があったことが伺える。まさに、モバイル機器がけん引した“半導体の10年の進化”を体現するようなスマートフォンだったのだ――。 ニッポンのお家芸“カメラ”にも押し寄せるスマホ用チップセットの波

ニッポンのお家芸“カメラ”にも押し寄せるスマホ用チップセットの波

リコーの360度全天カメラ「THETA」を取り上げる。2017年9月15日に発売されたばかりの最新モデル「RICOH THETA V」と従来モデルを比較していくと、外観にはさほど違いがないにも関わらず、内部には大きな変化が生じていたのだった――。 ムーアの法則は健在! 10nmに突入したGalaxy搭載プロセッサの変遷

ムーアの法則は健在! 10nmに突入したGalaxy搭載プロセッサの変遷

今回はSamsung Electronicsの最新スマートフォン「Galaxy S8+」に搭載されているプロセッサ「Exynos8895」を中心に、Galaxy Sシリーズ搭載プロセッサの進化の変遷を見ていく。そこには、ムーアの法則の健在ぶりが垣間見えた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増