窒素注入で低抵抗を実現したトレンチ型SiC-MOSFET:三菱電機が開発(2/2 ページ)

通電しやすい「高濃度層」の形成

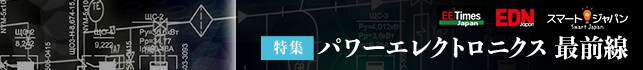

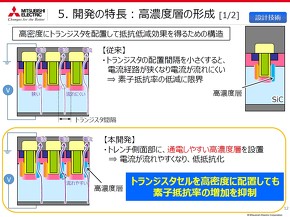

高濃度層の形成は、高密度にトランジスタセルを配置しても低抵抗を維持できるようにするための技術だ。先述した通り、トレンチ型ではトランジスタの配置間隔を狭くして、パワー半導体素子として高密度化できる点がメリットだが、間隔を狭め過ぎると、トランジスタセル間の電流が流れにくくなり、素子抵抗率を低く抑えることが難しくなる。そこで、トレンチの側面部(前出の「側面接地部」とは反対側)に窒素を注入し、通電しやすい高濃度層を形成することで電流を流しやすくした。その結果、高濃度層を形成しなかった場合に比べて、素子抵抗率を約25%低減できたという。

不純物を斜め上から注入する

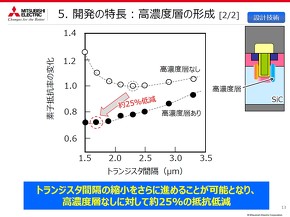

さらに三菱電機は、側面接地部や高濃度層を形成するために、トレンチの側壁に対して斜め上から不純物を注入する「斜め注入」を開発して適用した。トレンチ型SiC-MOSFETの量産時に、より簡単に、側面接地部と高濃度層を形成できることを狙ったという。

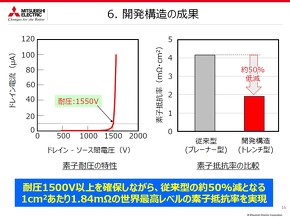

これらの技術により、開発したトレンチ型SiC-MOSFETでは、耐圧1500V以上を維持しつつ、素子抵抗率は、プレーナー型SiC-MOSFETの約半分となる1cm2当たり1.84mΩを実現したと、三菱電機は強調した。

三菱電機は、2021年度以降の実用化を目指して今回発表したトレンチ型SiC-MOSFETの開発を進める。適用する分野としては家電や産業用機器など、電圧が低い領域を挙げた。「電圧が高めの鉄道車両にも適用できないわけではないが、今回開発したトレンチ型SiC-MOSFETの特長を、より生かすことができるのは電圧が低い領域だ」(三菱電機)

素子のサイズについては「小型のものから大型のものまで試作しているが、5mm角が標準的になるのではないか」(同社)とした。

三菱電機は、プレーナー型SiC-MOSFETについては既に商品化しているが、次世代のパワー半導体素子では、ディスクリートでもモジュールでも、トレンチ型SiC-MOSFETの採用を増やしていくという。ただし、「プレーナー型からトレンチ型に置き換えていくわけではなく、プレーナー型にもニーズがあるので、両方を並行して生産していこうと考えている」と述べた。

関連記事

IGBTとIPM主軸に売上高2000億円超へ、大型投資も実施

IGBTとIPM主軸に売上高2000億円超へ、大型投資も実施

人口増加や経済成長、テクノロジーの発展に伴って世界のエネルギー消費量が増加を続けるなか、省エネ化/低炭素社会のキーデバイスとなるパワー半導体に注目が集まっている。今回、IGBTをはじめとするパワー半導体の主要メーカー、三菱電機の執行役員、半導体・デバイス第一事業部長、山崎大樹氏に話を聞いた。 パワー半導体が競演、「PCIM Europe 2019」レポート

パワー半導体が競演、「PCIM Europe 2019」レポート

「EE Times Japan」に掲載した主要な記事を、読みやすいPDF形式の電子ブックレットに再編集した「エンジニア電子ブックレット」。今回は、2019年5月7〜9日に開催された世界最大規模のパワエレ関連展示会「PCIM Europe 2019」の現地レポート記事をまとめた電子ブックレットを紹介します。 SiCパワー半導体市場、2024年までに20億米ドルに成長

SiCパワー半導体市場、2024年までに20億米ドルに成長

フランスの市場調査会社Yole Développement(以下、Yole)は、2019年7月、SiC(炭化ケイ素)パワー半導体市場が2024年までに20億米ドルに達する、という予測を発表した。Yoleはさらに、同市場が「2018年から2024年の間、年平均成長率29%で成長する」としている。 主流はシリコンパワー半導体、EV市場に期待大

主流はシリコンパワー半導体、EV市場に期待大

東芝デバイス&ストレージは、2019年4月、東京都内でパワー半導体に関する技術説明会を実施し、パワー半導体の市場予測や東芝のパワー半導体事業の現状などを説明した。東芝デバイス&ストレージでパワーデバイス技師長を務める川野友広氏は、現在の主流はシリコン製品であり、特に高性能が要求されるMOSFETとハイパワー製品(=IGBT)に注力するとしつつ、SiC(炭化ケイ素)パワーデバイスの将来性にも触れ、「パワー半導体事業は非常に安定した事業だ。今後も製品開発と投資を継続していく」と語った。 三菱電機、インバーター用パワー半導体モジュール

三菱電機、インバーター用パワー半導体モジュール

三菱電機は2019年8月、白物家電や産業用モーターのインバーター駆動用として小型パワー半導体モジュール「DIPIPM Ver.7」を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表