ラティス、28nmFD-SOIの新FPGAプラットフォーム:「エッジAIに最適」と強調(1/2 ページ)

Lattice Semiconductor(ラティスセミコンダクター)は2019年12月10日(米国時間)、28nm FD-SOI(完全空乏型シリコン・オン ・インシュレーター)を採用した新たな低消費電力FPGAプラットフォーム「Nexus」および、その最初の製品となる「CrossLink-NX」を発表した。

Lattice Semiconductor(ラティスセミコンダクター)は2019年12月10日(米国時間)、28nm FD-SOI(完全空乏型シリコン・オン ・インシュレーター)を採用した新たな低消費電力FPGAプラットフォーム「Nexus」および、その最初の製品となる「CrossLink-NX」を発表した。

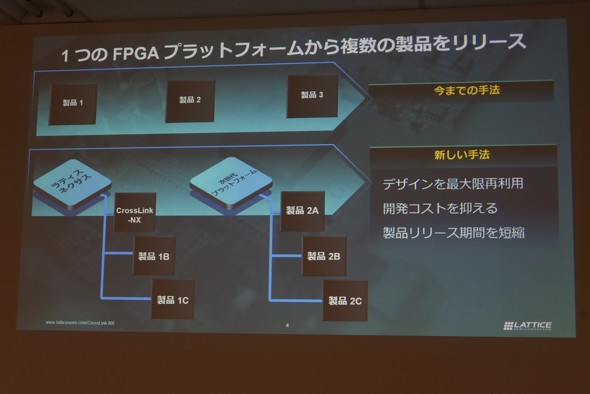

FPGA製品、プラットフォームでの展開に転換

ラティスセミコンダクターはFPGA製品の展開について、これまでのようなファミリーごとに製品を作っていく手法から、1つのプラットフォームで複数製品をリリースする新たな手法に転換。デザインを最大限利用することで、開発コストを抑えるとともに、製品リリース期間の短縮も図っていくという。今回発表したNexus以降についても、同様にプラットフォーム展開を行っていく予定だ。

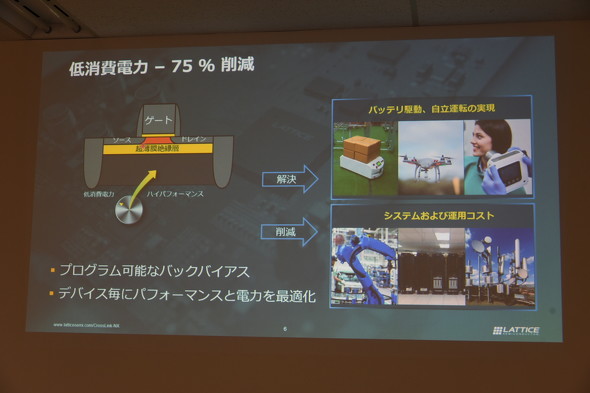

Nexusは、Samsung Foundryの28nm FD-SOIプロセステクノロジーを採用しており、バルク技術を採用した従来のFPGAと比較し、トランジスタのリーク電流を50%低減することが可能になっているという。また、同社のアジアパシフィック地域事業開発担当ディレクターを務めるYing Chen(イン・チェン)氏は、「FD-SOI採用によて、例えばハイパフォーマンスを目指すためには従来なら『プロセスを変えて新しいシリコンで』という形になったが、FD-SOIであればバックバイアスの電圧を変えるだけで対応ができる。デバイスごとにパフォーマンスと電力を最適化できることになる」とも強調した。

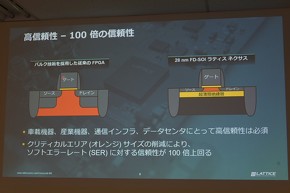

さらに、クリティカルエリアサイズが削減されるFD-SOIの採用によって、バルク技術を採用した従来のFPGAと比較しソフトエラーレートに対する信頼性が100倍上昇しているといい、「車載、産業機器や通信インフラ、データセンターなど信頼性が求められるアプリケーションに最適だ」としている。

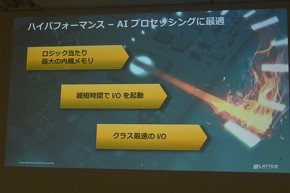

小型化については、4入力ルックアップテーブル(LUT4)を採用したことで、6入力ルックアップテーブル(LUT6)を用いた他社製FPGAと比べ10分の1のサイズになったと紹介。Chen氏は、「スピードはLUT6のほうが優れているかもしれないが、市場を調査のうえで、ニーズに十分こたえられると判断した」と話していた。また、ロジック当たり最大の内蔵メモリを搭載したほか、短時間でIOを起動できるよう設計しているなど、「高性能エッジAIプロセッシングに最適な製品となっている」とも強調していた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング