半導体産業はコロナに負けない! 製造装置市場の動向を読み解く:湯之上隆のナノフォーカス(28)(3/4 ページ)

3次元NAND効果

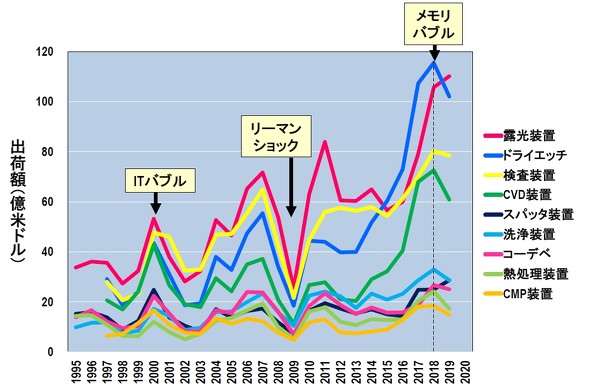

図4に、各種製造装置の出荷額の推移を示す。2015年に、それまで出荷額1位だった露光装置に替わって、ドライエッチング装置がトップに躍り出た。また、CVD装置の出荷額も急拡大し、2017年には露光装置や検査装置に接近するほどになった。

これは、本格的なビッグデータの時代を迎えて、データセンターの需要が急拡大し、サーバ用のメモリ市場が急成長したことに起因している。そのメモリの中でも特に、NANDが3次元化したことのインパクトは大きかった。

メモリ密度を毎年1.5倍ずつ高密度化するために、3次元NANDの積層数が、24層→32層→48層→64層→96層→128層と増大している。例えば、64層から96層に移行するには、単純計算で1.5倍の台数のCVD装置が必要になる。

またその際、必要なドライエッチング装置の台数は1.5倍どころではない。というのは、64層の3次元NANDのメモリホールを開口するのに約1時間かかっていた。しかし、孔が深くなるほど、指数関数的にエッチング速度が低下するため、96層のメモリホールの開口には、数時間ほどかかることになるからだ。

と言っても、96層(正確には92層)のメモリホールを一括加工しているのはSamsungだけであり、キオクシアなどの他社は、48層の2段積みで96層を形成している。それでも、48層のHARCエッチングを2回行うため、ドライエッチング装置の台数が2倍必要になる。

このように、NANDが3次元化し、その積層数が増大していくことにより、各種の製造装置が大量に必要になった。そのインパクトにより、2017年に、製造装置の出荷額がITバブルのピークを越えたと考えられる。

メモリ市場の急成長は2018年でピークアウトし、2019年はメモリ不況に陥った。しかし、2020年以降は、再びメモリ市場が成長し始め、製造装置の出荷額が増大すると予測される。

EUV効果

図4に示したように、2019年のメモリ不況により、多くの製造装置の出荷額が減少している。ところが、露光装置は出荷額が増大している。その結果、2019年に、露光装置が再び出荷額1位に返り咲いた。これは、1台160億円もする最先端露光装置EUVが、本格的に普及し始めたことによる。

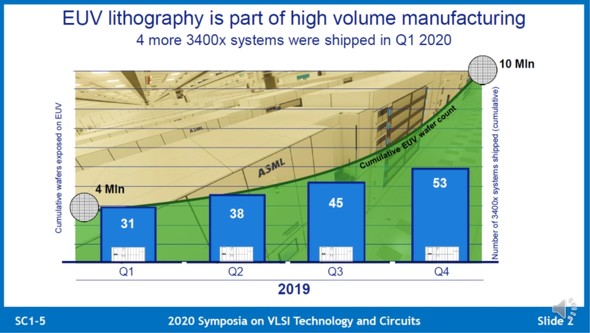

2020年6月に行われた「VLSIシンポジウム」で、ASMLは、2019年第4四半期に累計で53台のEUV(3400シリーズ)を出荷したことを発表した(図5)。この資料には、2020年第1四半期に4台追加されたことが書かれている。従って、2020年第1四半期時点で、累計で57台のEUVが出荷されたことになる。

図5:ASMLによるEUV露光装置の合計出荷台数 出典:Anthony Yen, ASML, “EUV Lithography and Its Application to Logic and Memory Devices”, VLSI 2020, SC1.5(クリックで拡大)

図5:ASMLによるEUV露光装置の合計出荷台数 出典:Anthony Yen, ASML, “EUV Lithography and Its Application to Logic and Memory Devices”, VLSI 2020, SC1.5(クリックで拡大)そして、驚くべきことに、2020年1月22日のWikiChip Fuseの記事によれば、2019年第4四半期時点で、ASMLのEUVの受注残が49台もあるとのことである(参考:WikiChip Fuse)。この内訳は、TSMCが20台、Samsungが20台、Intelが4〜5台、その他、MicronとSK hynixが数台ずつと推測している。

リソグラフィ業界に詳しい知人によれば、2020年以降にTSMCは、毎年20台以上ずつ、EUVを導入するという。また、これに対抗するために、Samsungも2020年から20台ずつEUVを導入していく計画であるらしい。このペースで行くと、この両社は、2025年にはEUVを100台以上稼働させている計算になる。このEUV効果により、今後も露光装置の出荷額が増大していくであろう。

そして、EUV周りの装置として、マスク描画装置、マスク検査装置、コータ・デベロッパなどの出荷額も成長していくことが期待される。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- NVIDIAとメモリ3社、世界半導体売上高の42%占める

- デンソー、ロームに対する株式取得提案を正式表明

- Armが半導体の自社開発に参入、AIデータセンター向けCPU発表

- イラン戦争の長期化が半導体業界に及ぼす深刻な影響

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- キオクシアがNanyaに774億円出資、DRAM長期供給契約を締結

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 東芝との協議やデンソー提案への対応、ロームが新声明

- 高NA EUVを「産業規模へ拡張」、imecがEXE:5200導入