Intel「10nmノード」の過去、現在、未来:苦戦を強いられた半導体の巨人(1/3 ページ)

Intelは現在、10nmプロセスの進化に向けて開発を進めているが、このプロセスノードは長年Intelを苦しめてきた。10nmにおけるIntelの闘いを振り返る。

この記事は、2020年7月17日発行の「EE Times Japan×EDN Japan 統合電子版7月号」に掲載している記事を転載したものです。

※記事を最後まで読むには、EE Times Japan読者登録(無料)が必要です。

世界最大の半導体メーカーであるならば、その地位を維持し、常に競合の一歩先を行き続けるために、野心的な目標を設定しがちになるものだ。Intelも、自社の10nmプロセス技術を軸に野心的な目標を設定したが、10nmの立ち上げが大幅に遅れた上に、ロードマップの変更を余儀なくされた。

加えて、いくつかの戦略を再検討する羽目にさえなった。Intelは現在、10nmプロセスの進化に向けて開発を進めているが、TSMCやSamsung Electronicsが7nm、6nm、5nm、さらにはそれ以下と称するプロセスに取り組んでいることを踏まえると、Intelは現時点で一体どの位置にいるのだろうか。

苦戦を強いられたIntel

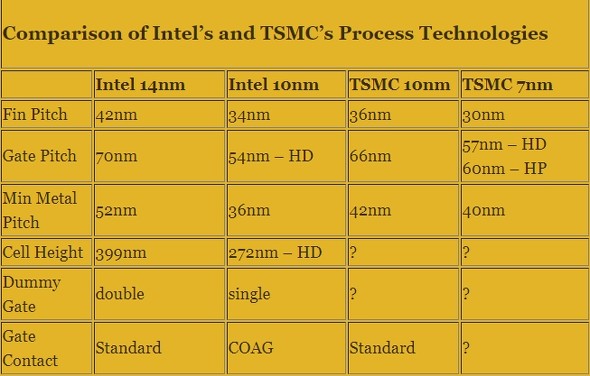

新しいプロセス技術を開発する場合、企業は性能/電力/面積(PPA:Performance, Power, and Area)に関して一定の目標を設定する。Intelは、プロセスとマイクロアーキテクチャを2年ごとに交互に一新する「チック・タック戦略」の下、PPAの全てにわたりプロセス技術を進化させてきた。Intelは10nm(「Intel 1274」としても知られる)において、14nmと比べトランジスタ密度を最大2.7倍、性能を25%向上することを目指していた。

Intelが公表した10nmの特長の多くは、TSMCの第1世代の7nm製造プロセス(N7)と似ているが、Intelは当初、TSMCのN7の量産開始より約2年早い2016年に、10nmデバイスの量産を始める計画だった。計画通りになっていれば、Intelは特にHPC(High Performance Computing)の領域において、競合先に対する優位性を得られていたはずだ。

Intelは、野心的なトランジスタ密度の向上を「ハイパースケーリング」と呼んでいたが、その後、歩留まりが予想より低く、コストが14nmより高かったことから、目標を見直すこととなった。一方で、10nmプロセスでは、「ムーアの法則」を持続させるためや、ダイサイズを小型に維持するため、そしてコストを削減するために、通常よりも積極的なスケーリングが必要となった。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

IntelとTSMCのプロセスの比較

IntelとTSMCのプロセスの比較