フィンFET(FinFET)の次に来るトランジスタ技術:福田昭のデバイス通信(303) imecが語る3nm以降のCMOS技術(6)(1/2 ページ)

今回からは「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を報告していく。

FinFETが限界に近づく3nm世代のCMOSロジック

半導体のデバイス技術とプロセス技術に関する世界最大の国際学会「IEDM(International Electron Devices Meeting)」は、「チュートリアル(Tutorials)」と呼ぶ技術講座を本会議(技術講演会)とは別に、プレイベントとして開催してきた。2020年12月に開催されたIEDM(Covid-19の世界的な流行によってバーチャルイベントとして開催)、通称「IEDM2020」では、合計で6本のチュートリアル講演が実施された。その中で「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」が非常に興味深かった。講演者は研究開発機関のimecでTechnology Solutions and Enablement担当バイスプレジデントをつとめるMyung‐Hee Na氏である。

そこで本講座の概要を本コラムの第298回から、シリーズでお届けしている。なお講演の内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演の内容を適宜、補足している。あらかじめご了承されたい。

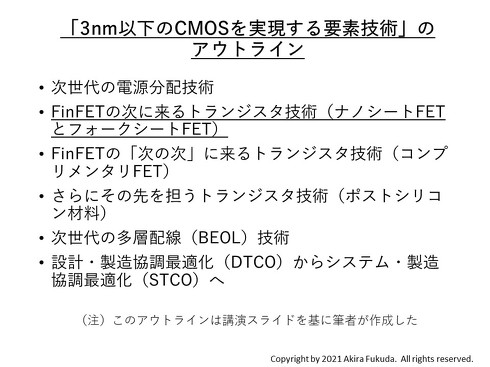

本シリーズの前回までは、始めのパートである「次世代の電源分配技術」に関する講演部分の概要をご紹介した。今回からは、2番目のパートである「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分をご報告していく。

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回までは始めの「次世代の電源分配技術」に関する講演部分の概要をご紹介した。今回からは「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を報告していく(クリックで拡大)

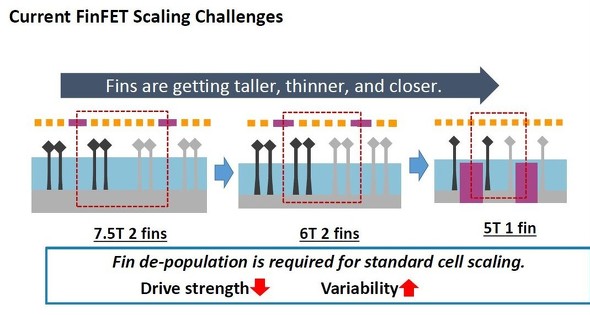

チュートリアル講演「Innovative technology elements to enable CMOS scaling in 3nm and beyond - device architectures, parasitics and materials(CMOSを3nm以下に微細化する要素技術-デバイスアーキテクチャと寄生素子、材料)」のアウトライン。講演スライド全体から筆者が作成したもの。前回までは始めの「次世代の電源分配技術」に関する講演部分の概要をご紹介した。今回からは「FinFETの次に来るトランジスタ技術(ナノシートFETとフォークシートFET)」の講演部分を報告していく(クリックで拡大)既にご説明してきたように、FinFET(フィンフェット)をトランジスタとするCMOSロジックは、フィンのピッチを詰めるとともにフィンを高くし、フィンと平行な方向の最下層金属配線の本数(トラック数)を減らすことで基本セル(スタンダードセル)を縮小してきた。例えば7.5トラックの基本セルでは、フィンが2枚のpチャンネルFinFETとnチャンネルFinFETによってCMOSインバータを構成していた。次の世代では、フィンの枚数を維持しながら、トラック数を6トラックに減らすことで基本セルの面積を縮めた。

さらに次の世代では、トラック数を5トラックに減らすとともにフィンの枚数を1枚に減らすことで基本セルの面積を減らすことが考えられている。フィンの枚数を減らすのはpチャンネルFinFETとnチャンネルFinFETの間の距離(素子分離を維持可能な距離)を一定に維持するためである。

ここで問題となるのはFinFETに対する要求仕様が世代交代とともに一気に厳しくなっていくことだ。フィンの枚数を減らすことは、FinFETの電流駆動能力を減らすことになる。これを緩和するためには、フィン1枚当たりの電流駆動能力を上げなければならない。またフィンを薄くしたり、ピッチを詰めたりすることにより、加工寸法や不純物濃度などのばらつきによる影響が大きくなってしまう。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増