チップレットvs. 1シリコン化、AMDとIntelの戦略を読み解く:この10年で起こったこと、次の10年で起こること(68)(2/3 ページ)

Ryzenの新旧世代を比較する

図3は、前世代「Ryzen 9 5950X」と新チップであるRyzen 9 7950Xの面積とチップ配線ありの外観比較である。面積は平方ミリメートル単位での数値ではなく、Ryzen 9 5950Xを1とした数値を掲載した。

新旧IOの外観、アスペクト、新旧CPUの外観、アスペクトはほぼ同じものになっている。GlobalFoundriesの12nmで製造された前世代のIOシリコンに対して、新世代のIOシリコンはTSMCの6nmを活用するにもかかわらず、わずかに3%面積が縮小されたものになっている。

PCI Expressが4.0から5.0、DDRメモリのインタフェースもDDR4からDDR5に変更されていて、大幅な性能/機能アップを行っているので、12nmから6nmと、より微細化した製造プロセスを用いていても面積はほとんど変わっていないわけである。

また、Ryzen 9 5950Xには搭載されていなかったGPU「RDNA 2」も、Ryzen 9 7950XのIOシリコンには搭載されている。CPUシリコンのアーキテクチャが「Zen3」からZen4に変わっているので、CPU部の比率は前世代に比べて若干大きめになっている。

CPUシリコンは左右にCPUコアが4個ずつ、計8個並び、8コアCPUに囲まれる形でL2(計16MB、前世代では8MB)、L3 64MB(L3のサイズは前世代と同じ)が配置されている。前世代のRyzen 9 5950Xの面積を1とすると、Ryzen 9 7950Xでは0.83と、性能やメモリ容量の拡大にもかかわらず、大幅な面積削減を実現しているわけだ。図3の7nm Area 1.00、5nm Area 0.83と書かれた部分がL2、L3キャッシュ、文字の左右がCPU8個になるので、CPU部とメモリ部の比率が大きく変わったことが良く分かる。製造プロセスの微細化によってメモリは縮小し、CPUアーキテクチャの更新によってロジック部は増加したものになっている。

Intelの第13世代Coreシリーズを比較する

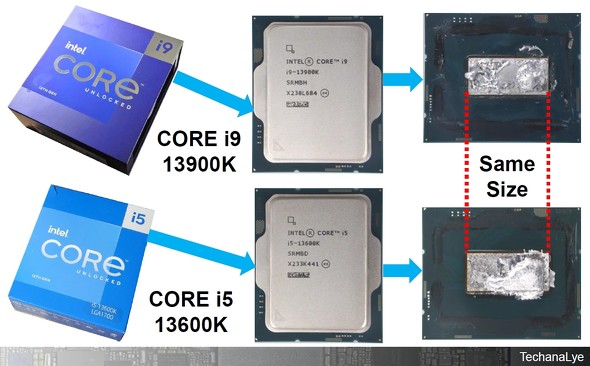

図4は、2022年10月に発売されたIntelの第13世代Coreシリーズのうち、ハイエンドの「Core i9 13900K」と、同時に発売されたミドル仕様の「Core i5 13600K」である。AMDのRyzen 7000シリーズとほぼ同じハイエンドとミドルのラインアップを同時発売でそろえている。ハイエンドもミドルも、LIDを外すと同じサイズのシリコンであることが確認できる。AMDがシリコンを組み合わせることでラインアップを作っているのに対して、Intelは1つのシリコンで(機能を止める、あるいは製造不良部を使わないなど)使い分けをし、1シリコンでCPU、IO、GPUを実装しているという大きな違いがある。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」