ラティス、中規模FPGAプラットフォームを発表:第1弾はLattice Avant-Eファミリー

ラティスセミコンダクターは、中規模のロジックセル数を必要とする用途に向けたFPGAプラットフォーム「Lattice Avant」を発表。その第一弾として「Lattice Avant-E」のサンプル出荷を始めた。同等クラスの製品に比べ、高い電力効率やコネクティビティ、演算性能を実現した。

エッジ端末などの高機能化/高性能化に対応

Lattice Semiconductorの日本法人であるラティスセミコンダクターは2022年12月6日、中規模のロジックセル数を必要とする用途に向けたFPGAプラットフォーム「Lattice Avant」を発表。その第一弾として「Lattice Avant-E」のサンプル出荷を始めた。同等クラスの製品に比べ、高い電力効率やコネクティビティ、演算性能を実現した。

ラティスセミコンダクターは、エッジ端末などに向けて28nm FD-SOI(完全空乏型シリコン・オン・インシュレーター)プロセスを適用したFPGAプラットフォーム「Nexus」を展開している。競合製品に比べて、「消費電力は4分の1」「コネクティビティは2倍」「パッケージサイズは10分の1」という特長を持った製品である。ただ、ロジックセル数が最大100K個と比較的小規模であった。

そこで今回、同社の強みを生かしつつ、顧客からの要望が強い中規模FPGA「Lattice Avant」を新たに追加した。エッジ端末などにおけるAI処理など、FPGAにもさらなる高機能化/高性能化が求められているからだ。Lattice Avantは、TSMCの16nm FinFET技術を用いて製造する。高い電力効率や小型サイズを維持しつつ、Nexusに比べて、「ロジックセル数は5倍に、帯域幅は10倍に、性能は30倍に、それぞれ向上させた」という。

ロジックセル数が500K規模の競合製品と比べても、Lattice Avantは電力消費が半分かそれ以下で、放熱設計などを容易にした。シリアル帯域幅も最大2倍に拡大、高速なスループットを低消費電力で実現した。さらに、パッケージの外形寸法は13×13mmで競合製品に比べると最大6分の1も小型である。

この他、レーン当たり最大25Gビット/秒のコンフィギュアブルSERDESや、PCIe Gen 4×8コントローラー、LPDDR4やDDR5などの高速メモリインタフェースなどに対応している。また、AI推論向けに最適化したDSPや、セキュリティエンジンなども内蔵した。

顧客のシステム開発を支援する設計ツールやレファレンスデザイン/SDK、IPコアなどは、使い慣れた既存のソフトウェアソリューションを活用することができる。

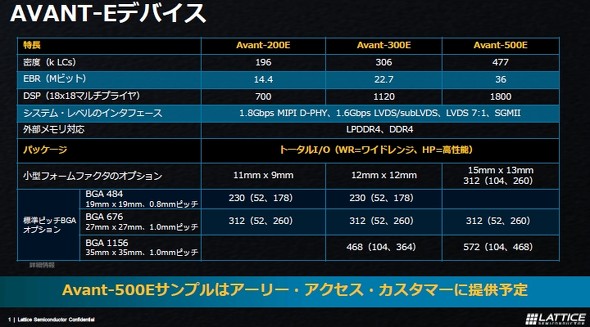

Lattice Avantの第一弾となるLattice Avant-Eファミリーは、仕様が異なる3製品を用意した。ロジックセル数の違いで見ると、477K個の「Avant-500E」、306K個の「Avant-300E」、196K個の「Avant-200E」である。2023年以降は、新しいLattice Avantシリーズも順次投入していく計画だという。

関連記事

複雑化するシステム制御を簡単に、LatticeのFPGA

複雑化するシステム制御を簡単に、LatticeのFPGA

Lattice Semiconductor(以下、Lattice)の日本法人であるラティスセミコンダクターは2022年5月31日、28nm FD-SOI(完全空乏型シリコン・オン・インシュレーター)プロセスを適用したFPGAプラットフォーム「Nexus」の第5弾製品として、「MachXO5-NX」を発表した。 ラティス、新sensAIソリューションスタックを発表

ラティス、新sensAIソリューションスタックを発表

ラティスセミコンダクター(以下、ラティス)は、次世代のエッジデバイスに向けて、FPGA「Nexus」上で動作する「sensAIソリューションスタック」の最新版(v4.1)を発表した。 帯域幅とメモリを増大したエッジAI向けFPGA

帯域幅とメモリを増大したエッジAI向けFPGA

Lattice Semiconductor(以下、Lattice)の日本法人であるラティスセミコンダクターは2021年6月29日、エッジアプリケーション向けの汎用FPGAとして「CertusPro-NX」を発表した。 384ビット暗号対応のFPGA、「PFR」の実装が容易に

384ビット暗号対応のFPGA、「PFR」の実装が容易に

Lattice Semiconductorの日本法人であるラティスセミコンダクター(以下、ラティス)は2020年12月10日、サイバーレジリエンス向けに、セキュリティ機能を強化したFPGA「Mach-NX」を発表した。2019年に発表した「MachXO3D」の機能をベースとしたもので、MachXO3Dに続く第2世代品となる。 AMDによるXilinx買収で、Intelとの競争が激化

AMDによるXilinx買収で、Intelとの競争が激化

AMDが約350億米ドルでXilinxを買収することで、CPUシェア第2位のAMDとIntelとの競争が激化するとが予想される。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 村田製作所、25年度は売上高が過去最高 データセンター向けは70%増

Lattice Avantの外観 出所:ラティスセミコンダクター

Lattice Avantの外観 出所:ラティスセミコンダクター