最新チップを徹底比較! 〜最新スマホから復刻版ゲーム機まで:この10年で起こったこと、次の10年で起こること(73)(2/3 ページ)

「Dimensity 9200」と「Snapdragon 8 Gen 2」のCPUを比較する

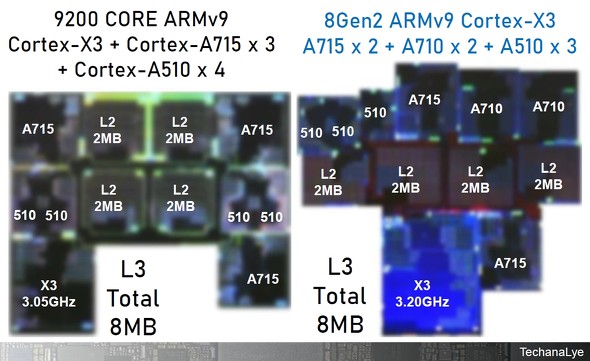

図1は、Dimensity 9200の3階層CPUと、Snapdragon 8 Gen 2の4階層CPUの比較である。サイズはほぼ同じ。最上位CPUには、Armの「Cortex-X3」コアがともに採用されている。最も面積が大きいCPUである。チップでは多くの電流を流せると高速化するので部品が大きくなってしまう。

Cortex-X3の動作周波数は、Dimensity 9200の3.05GHzに対して、Snapdragon 8 Gen 2では3.20GHzと5%ほど高い。前述のようにQualcommは高速向け製造プロセスを用いていないので、大きな部品を使うことで高い周波数を実現しているわけだ。そのため、QualcommのCortex-X3は、MediaTekに比べて1.3倍ほど大きなものになっている。最高速のCortex-X3以外は2GHz台と、周波数が限界まで高くなく処理速度に余裕があるので、MediaTek、Qualcommともにほぼ同じサイズに収まっている。

Qualcommは、Cortex-X3に加え、最新のミドル性能のCPUコア「Cortex-A715」を2基、1世代前のミドルCPUコア「Cortex-A710」を2基、高効率CPUコア「Cortex-A510」を3基の1-2-2-3階層で8コア。アプリケーションに応じて速度と電力を最適化させているわけだ。MediaTekは1-3-4という構成になっている。成熟したスマートフォンプロセッサとはいえ、先行する2社の中身には今なお大きな差が存在していることが分かる。

IntelとAMDの最新CPUを比較する

表2は、2022年秋にIntelから発売された第13世代の「Core i9 13900K」とAMDの「Zen 4」世代のCPU「Ryzen 9 7950X」の断面解析の比較である。

Core i9 13900KとRyzen 9 7950Xの平面解析は、本連載の「チップレット vs 1シリコン化、AMDとIntelの戦略を読み解く」(2022年11月公開)に掲載されているので併読いただきたい。また弊社では、HPC向けのプロセッサとして、AMD「EPYC」やIntel「Xeon」も今夏に向けて解析を行っているところである。プロセッサとパッケージを丸ごと切断し、研磨し、顕微鏡やSEMを用いて断面解析(配線幅、スペース、層数、接続部の構造など)を行った結果、AMDはTSMCの5nm、Intelは同社の「Intel 7」(10nm世代相当/「10nm Enhanced SuperFin」)と世代差はあるものの、シリコンの配線層数(グローバル層と呼ばれる長距離配線用は考え方が異なるので厚さが全く別物)は同じであった。

一方、パッケージの配線層数はIntelが10層に対して、AMDは12層と2割多い。パッケージでもシリコンでも配線層数が増えると製造工程、コストともに増える。AMDのチップレットはシリコンを再利用できる(CPU数を増減することでハイ/ミドル/ローを作り分けできる)点で優れているが、パッケージ層数が増える、シリコンテストが増えるなどの「増加」要因も多く持っているわけだ。チップレットはポジティブ面も大きいがネガティブ面もあるので、万能ではないという認識を持つことが必要だ。

NVIDIAとAMDのGPUを比較する

表3は、NVIDIAが2022年末に発売した「Ada Lovelace」世代の最上位GPU「RTX 4090」とAMDの「RDNA 3」世代の最上位GPU「RX 7900 XTX」の比較である。

NVIDIAはTSMCの4nmを用い、1シリコンに763億個のトランジスタを搭載する。一方、AMDは7個のシリコンを組み合わせたチップレット構成を取っていて、GPUはTSMCの5nm、キャッシュ用のSRAMはTSMCの6nmで製造している。これをパッケージ内で組み合わせ、トータルで577億個のトランジスタを搭載している。

取り出したシリコンは電子機器を用いて測長しているので各社が発表する数字と微妙に異なる場合もある(発表数字はスクライブなどの面積を含まないものがある)。弊社では、販売されるシリコン面積を採用している。NVIDIA、AMDともに500mm2超えと巨大だ。単純計算になるが、各社が発表したトランジスタ数を用いて算出すると、NVIDIAは0.124 Billion Transistor/mm2(1億2400万トランジスタ/mm2)、AMDは、0.109 Billion Transistor/mm2(1億900万トランジスタ/mm2)となる。AMDはCPUではIntelと、GPUではNVIDIAと競い合っているので、製品ラインアップを作り分けしやすいチップレットを最大限活用し、開発効率を上げている。

また今後はSRAMとロジックが同じ比率で縮小しなかった場合、シリコン効率(プロセスを進化させてもほとんど面積が変わらないものは効率が低い)を最適化するために外キャッシュはプロセッサと別シリコン化される可能性は高くなると思われる。また外部インタフェース用のPHYもプロセッサから別シリコンに移すとシリコン効率が良いケースも増える可能性が高いので、3nm、2nm世代では多くのメーカーがチップレットを用いていくことになるだろうと思われる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待