CXL/UCIeから考える光インターコネクト技術:光伝送技術を知る(22) 光伝送技術の新しい潮流と動向(3)(2/4 ページ)

Compute Express Link(CXL)

まず、前述のDGXのスケールアウトに相当する、xPU間(Compute Network)とxPU-メモリ間(Data Network)の広帯域な接続(密結合)の実現に注目したい。前回述べたBackend Networkである。それを可能にするCXLの規格化[3]が進められている。

CXL ConsortiumはCPU、メモリ、アクセラレーター間の高効率/高速/大容量接続のオープン標準規格を目指し、Intelが主導して2019年に設立された。規格のバージョンとして、1.0/1.1/2.0、そして2022年8月に3.0を発行した。200社以上のメンバーを有し(2023年6月時点)、有力なデバイスメーカー、システム企業、ユーザー企業がボードを務める。主要標準規格団体であったGen-ZやOpen CAPIを取り込み、多くの支持を得ている(他の競合するCCIXは休業状態)。

Composable Disaggregated Systemでは、仕事(ワークロード)ごとにCompositeされたxPUとメモリとのアクセスが本質である。そのメモリも、DRAM PoolからNVMe SSDまでさまざまな種類の混在を目指している。いわゆるGeneral Fabric Attached Memory(G-FAM)も包含している。さらに、効率よく利用するためPool内のメモリ(空間)をワークロードごとに割り当て可能なだけではなく、同じメモリ空間を複数のホストCPUが共有することも可能だ。

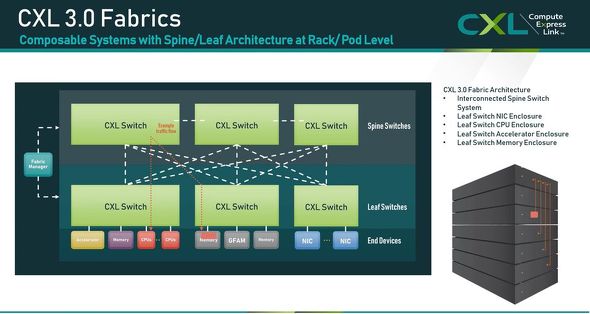

CXL 3.0では図2に示すようにマルチレイヤースイッチネットワークも可能で4096個のNodeを接続できる[4]。CXLは今後の拡張もあるとのことで、さらに注目していきたい。

[4]“CXL 3.0: Enabling composable systems with expanded fabric capabilities,” CXL Consortium Webinar, Oct. 6th, 2023

CXLの物理層

CXLインタフェースは光インターコネクトの応用ターゲットである。公開されているCXLのSpecification 3.0[5]によれば、物理層(PHY:Physical Layer(正確にはFlex Bus Physical Layer))はPCIe 5.0と6.0のPHYをベースにしている。PCIe 6.0は2022年1月に公表され、同年8月に発表されたCXL 3.0に採用されている。今後もPCIe 7.0が公表されれば追加されると考えられる。

[5]“Compute Express Link (CXL) Specification,” Revision 3.0, Version 1.0, August 1, 2022

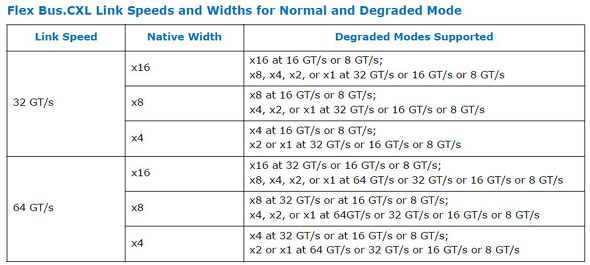

その伝送速度とデータ幅を表1に示す。PCIe同様、伝送速度は32GT/s(PCIe 5.0)と64GT/s(PCIe 6.0)、ビット幅は16が基本である。T/sはbit/sに置き換えてよい。最大伝送速度は32Gbit/s ×16=64GB/s(PCIe 5.0)と64Gbit/s ×16=128GB/s(PCIe 6.0)である。

特徴として、最大性能が達成されないときは伝送速度とビット幅をそれぞれ半分に、次々と縮退できる。最小は伝送速度8GT/s(Gbit/s)でビット幅4である(PCIeと異なる)。これは、光インターコネクト使用時にレーザーが故障した場合、システム性能は低下するかもしれないが、ジョブを継続できるということだ。光インターコネクトの弱点である故障率の要求を緩和できると考えられる。

光インターコネクトへの要求は、伝送速度64Gbit/sから8Gbit/sあるいは、32Gbit/sから8Gbit/sに対応できるレーン数16の光モジュールである。また、PCIe 7.0が公表される2025年には128Gbit/s ×16を実現しなければならない。

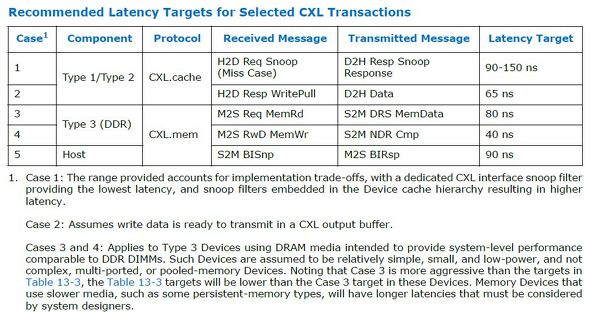

表2は、Specification 3.0に示されているレイテンシのターゲットだ。40〜150ナノ秒という数字が見える。現行のガラスファイバーの伝達時間は約5ナノ秒/mであるので、8mで40ナノ秒である。Rack-Scaleを想定した規格であることが分かる。また、150ナノ秒は30mに相当するので光インターコネクトの伝送距離は30m以下を想定して良い。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼