多チャンネル光インターコネクトの光デバイス技術:光伝送技術を知る(24) 光伝送技術の新しい潮流と動向(5)(2/3 ページ)

多チャンネル化と光多重化技術

光通信には「波長多重技術」という、波長が異なる複数の信号を1本のファイバで伝送する技術がある。Course Wavelength Division Multiplexing(CWDM)という世界標準波長から4波長選んだCWDM-4方式は、40G以降のSMF(シングルモードファイバ)光トランシーバーで最大の市場シェアを持つ方式だ。これを利用すれば、16チャネルは4心のCWDM-4、64チャネルは16心のCWDM-4を伝送するファイバアレイで実現できる。

このように、波長多重は多チャンネル化の手法として有望である。さらなる多チャンネル化をにらんだ波長の新しい規格を定義するCW WDM MSAも結成されている[8]。32波長多重までが定義され、2021年6月に仕様1.0が公開された。波長数を増やすと容量は増えるが、波長の安定性などの技術的課題や異なる波長の在庫管理などの製造や波長数増によるコストの課題などを解決しなければならない。

[8]参考URL:https://cw-wdm.org/

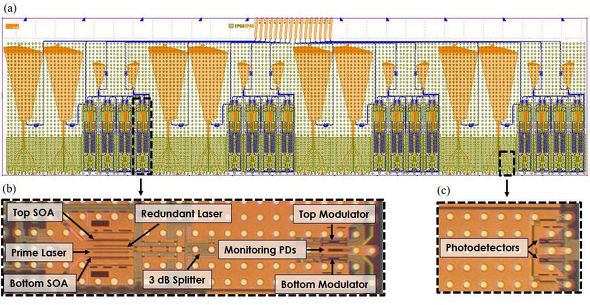

図2は、1波長当たり100Gbit/sのCWDM-4(Ethernet 400GBASE-FR-4)を8心ファイバアレイで伝送する32チャネルSi-photonicsトランシーバーチップである。Skorpionsが開発した[9]。上部がレイアウト図、下部がチップ写真である。“うちわ”のような形の所が、CWDM-4の波長多重分離回路である。大きなうちわが受信の波長分離回路、小さなうちわが送信の波長多重回路だ。波長が異なる4組の送受信回路(1組は図2下部の写真)と波長多重分離回路のセットが8個、約460umピッチで並んでいて、チップ幅は30.1mm。Shoreline Densityは3200Gbit/s÷30.1mm=106Gbit/s/mm、bi-sectionで212Gbit/s/mmとなる。

発表では、送受信回路とCWDM-4の多重分離部の配置を変えることで、チップ幅を19.2mmにできることを示した。幅を縮める代わりに長さは1mm程度長くなるという。この時のShoreline Densityは167Gbit/s/mm、bi-sectionで333Gbit/s/mmに改善される。

ちなみにNominal値ではあるがこのチップのEnergy Efficiencyは2.1pJ/bitという。しかし、各送信ブロックのオンチップレーザーと光増幅器が1.8pJ/bitと大部分を占めており、課題も見えている。

[9]Damien Lambert, et al, “3.2Tb/s Heterogeneous Photonic Integrated Circuit Chip in a Co-Packaged Optics Configuration,” OFC 2023, W3D.2

さらに、密度を高める工夫をしているのが、Micro-ring Resonator(MRR)を波長選択変調器と受信フィルターに利用した方式である。AyarLabsが有名だ(DARPA CHIPS、DARPA PIPES、ARPA-Eの支援を受けているという)[10]。

図1にもあったMRRは名前の通りリング状をした、光波長(周波数)レベルの共振器である。MRRと光導波路を光学的に結合させると、光導波路を通過する光の波長と共振波長が一致する時、MRRがその光を吸収する。MRRの共振波長は電気信号で変化させることができるため、共振波長を通過光の波長に合わせたり(MRRが光を吸収するため光信号OFF)、外したり(光信号ON)して変調を行うことができる。受信でもMRRと光導波路を光学的に結合させ、MRRを通過光(受信光)の特定波長に共振するように設定し、その波長の通過光を吸収・光電変換を行い、電気信号を得る。

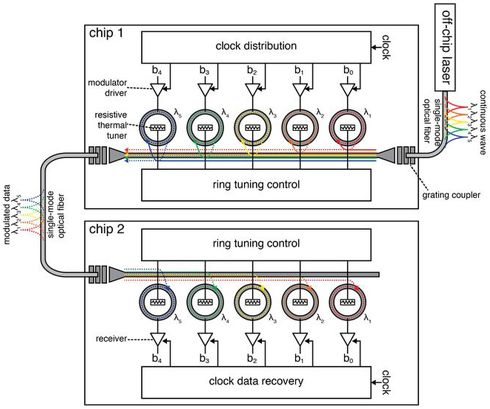

図3に、[10]に記載されたAyarLabsの方式の原理図を示す。右のチップ外光源(Off-chip laser)から、多重化された5つの異なる波長の光が入力される。送信部では、5つの波長に対応したMRRが、1本の導波路にタンデムで配置されている。それぞれのMRRは、5つの入力波長の一つで共振変調し、他の波長には影響がないように設計されている。受信も同様に、1本の導波路上に5個のMRRをタンデムに並べている。それぞれの共振波長の光信号のみを吸収し(他の波長はスルー)、光電変換を行い、電気信号を得る。

この方式のメリットは、MRRのサイズが直径10μmと小型であり、それをタンデムに並べることで集積密度を大幅に高められることだ(他の方式は数百マイクロメートル)。

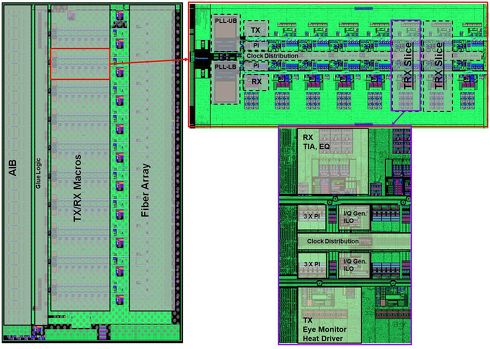

図4は、この技術を用いたAyarLabsの80チャネルトランシーバーチップである。このチップにはブロックが10個あり、それぞれのブロックは、8波長のMRRを使用した8チャネル波長多重送受信が可能で、1本のファイバに接続される。さらに、インタフェースを含む送受信の電子回路も同一チップに集積化されている。1ファイバ当たり256Gbit/sなので、1チャネル当たり32Gbit/sであり、このチップの伝送容量は2.56Tbit/sとなる。

チップの幅は8.86mmと報告されていて、チップのShoreline Densityは289Gbit/s/mm、bi-sectionで578Gbit/s/mmとなる。最近のホームページではファイバ本数は8本でShoreline Densityは228Gbit/s/mmとなっている。また、Energy Efficiencyは、<5pJ/bitと報告されているが、Off-chip laserの消費電力が含まれているかどうかは不明だ。

この方式は、Shoreline Densityを高める一つの手法として注目されているが、共振波長の温度依存性や製造ばらつき、共振波長付近の帯域低下など共振に関する課題が大きく、挑戦が続いている。

[10]M. Wade, et al, “TeraPHY: A Chiplet Technology for Low-Power, High-Bandwidth In-Package Optical I/O,” 2019 IEEE Hot Chips 31 Symposium (HCS)

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- 「データの死蔵に耐えられないエンジニア」がたどり着いたMASの沼