「FinFETの終えん」に備える 今後10年でGAAへの移行が加速?:技術的な課題は山積も(1/2 ページ)

10年以上、先端半導体をけん引してきたFinFETだが、今後は新しいトランジスタ構造であるGAA(Gate-All-Around)への移行が本格化すると考えられる。

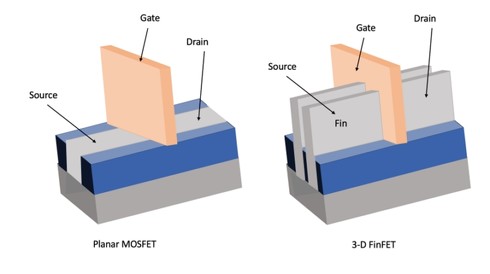

FinFETは今から10年以上前に登場し、チップの設計を再定義した。この非プレーナ型トランジスタは、現在も非公式の業界標準とされているが、今後は新しいテクノロジーであるGAA(Gate-All-Around)技術への移行が加速する可能性がある。エレクトロニクスエンジニアは、来るべき変化に備える必要がある。

FinFETを利用した最初のチップが2011年に登場し、半導体は25nmプロセス以下の領域に足を踏み入れることができた。このアーキテクチャは当時、「ムーアの法則」にとってある種の救いとなった。というのも、プレーナ型トランジスタはリーク電流が大きすぎて、100nm以下のジオメトリでは持続可能ではなかったからだ。

しかし、FinFETは現在、その前身となるプレーナ型技術と同じ問題に直面している。デバイスのフォームファクタが縮小し、性能要求が増大し続けていることから、リーク電力と信号干渉の問題が一般的な障害になりつつあるのだ。このため、半導体業界の多くの主要プレーヤーたちが、代替となるトランジスタアーキテクチャについて検討し始めているところだ。

FinFETは前身と比べて有用だが、より小さいジオメトリでは電力ルーティングに関する制約が厳しい。エンジニアは通常、この制約を、異なるチャンネル幅とスペーシングで回避している。この戦略は、多くのアプリケーションにおいてうまく対応することができるが、限界がある。

FinFETでは構造上、各チャンネル間のスペースを十分に確保する必要がある。結果的に、それぞれのフィン間隔は15nm〜20nmであるため、エンジニアはすぐにスケーラビリティの問題に突き当たることになる。そもそもチャンネル数を追加することは、非アクティブな領域を追加するということを意味し、電流ルーティングと物理的なスペースのトレードオフが生じることになる。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- ソニーセミコンCTOに聞く――イメージセンサー技術革新の核

- 「膿み出し切った」SiC関連減損で過去最大1584億円赤字 ローム

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- パワー半導体3社連合とデンソー提携のアナログ「両軸を強化」 ローム社長

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- JDI、25年度Q4は4年ぶり黒字 上場廃止は「必ず阻止」

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点