シリコン貫通電極ウエハー全自動研削装置を開発:3次元実装技術の普及を後押し

岡本工作機械製作所は、Si(シリコン)ウエハーの裏面からSi貫通電極を露出させることができる「Si貫通電極ウエハー全自動研削装置」を開発した。同装置を用いると、Si貫通電極の形成プロセスを効率化でき、3次元実装した半導体デバイスのコスト低減や歩留まりを向上させることが可能となる。

Si貫通電極形成プロセスを効率化、コスト低減や歩留まり向上が可能に

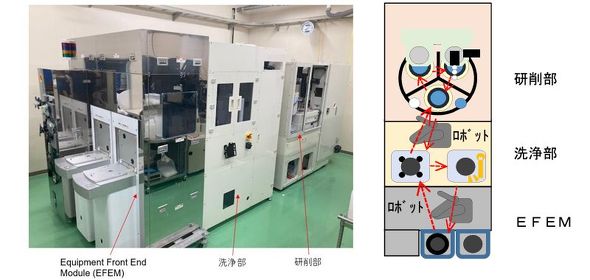

JST(科学技術振興機構)と岡本工作機械製作所は2024年10月29日、Si(シリコン)ウエハーの裏面からSi貫通電極を露出させることができる「Si貫通電極ウエハー全自動研削装置」を開発した。同装置を用いると、Si貫通電極の形成プロセスを効率化でき、3次元実装した半導体デバイスのコスト低減や歩留まりを向上させることが可能となる。

開発した装置は、産業技術総合研究所先端半導体研究センターの渡辺直也主任研究員による研究成果を基に、JSTの支援を受け、岡本工作機械製作所が実用化に向けた開発を2016年より行ってきた。そして、今回の研究成果をJSTが成功と認定した。

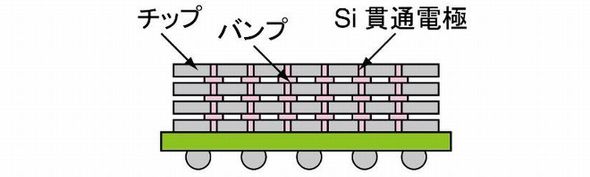

半導体回路は微細化による高性能・高機能化が限界を迎えつつある。こうした中、半導体回路の性能向上を実現する方法の1つとして、半導体チップを立体的に集積する3次元実装技術が注目されている。半導体チップにはCu(銅)などを用いてSi貫通電極を形成し、バンプと呼ばれる接合用電極を用いて垂直方向に積層する技術である。

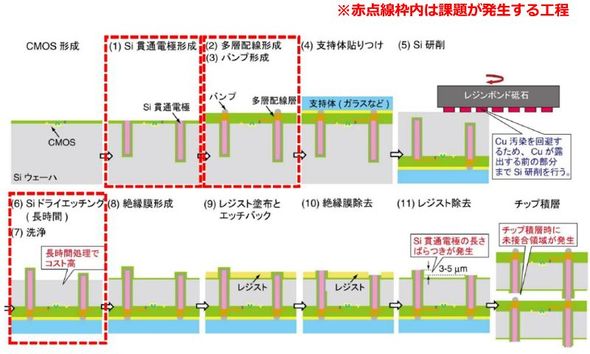

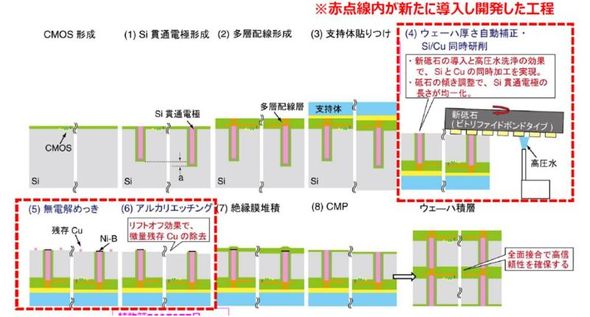

Si貫通電極を形成する方法は、主に2種類ある。その1つが微細化に対応しやすい「ビアミドルプロセス」である。ところがこの方法は、Siウエハーを薄くしてSi貫通電極をウエハー裏面から露出させるためにSiとCuを同時に研削すると、砥石にCuが目詰まりして研削性能が低下することがある。SiウエハーにCuが付着してチップの品質が低下するという課題もあった。

これらの課題を解決する方法は現在もあるが、工程が複雑となりコスト高の要因ともなっていた。このため、これらの方法を適用できるのが高価なデバイスに限られていた。しかも、深掘りエッチングの工程でSi貫通電極の長さにばらつきが生じ、歩留まりが低下する原因にもなっていた。

そこで今回、「SiとCuの安定的かつ精緻な同時研削技術」や「Siウエハー上の残留Cuを除去する技術」を開発した。これらの技術を採用することで、Si貫通電極形成においてビアミドルプロセスの効率を向上させるとともに、ウエハーレベルでの直接積層を可能にした。

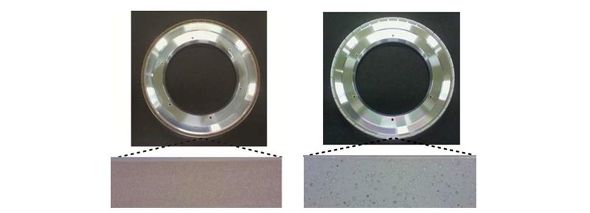

具体的には、目詰まりしにくい研削砥石を開発した。その上、研削時にCuが砥石に付着した場合でも、高圧水で洗浄することによりCuを除去できる技術を開発した。また、加工中は厚み測定器(IRセンサー)でリアルタイムに形状を測定し、研削ヘッド(砥石)の傾きを自動補正する研削方法を開発した。これにより、Si貫通電極の長さに関するばらつきを極限まで抑えた。

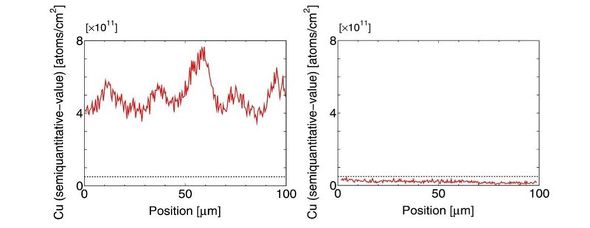

さらに、Siウエハー上の残留Cuを除去するため、SiとCuの同時研削で露出したSi貫通電極のCu面に対し、無電解ニッケル−ボロン(Ni-B)めっきで表面保護した後、Siウエットエッチングで処理した。この方法でSi貫通電極部分からCuが溶け出すことを防ぎ、Si上の残留Cuを一般的な金属濃度以下まで除去することに成功した。

関連記事

交互積層型の電荷移動錯体で高伝導化に成功、有機電子デバイスへの応用に期待

交互積層型の電荷移動錯体で高伝導化に成功、有機電子デバイスへの応用に期待

東京大学らの研究グループは、ドナーとアクセプターの分子軌道を混成することで、交互積層型電荷移動錯体の高伝導化に成功した。大量合成が可能な塗布型有機伝導体材料として、有機電子デバイスへの応用に期待する。 乾電池1本(1.5V)で発光する青色有機ELを開発

乾電池1本(1.5V)で発光する青色有機ELを開発

東京工業大学や富山大学、静岡大学らの研究グループは、電圧1.5Vの乾電池1本で発光させることができる「青色有機EL」の開発に成功した。開発した有機ELは、青色発光(波長462nm)を印加電圧1.26Vで確認、1.97Vでは発光輝度が100cd/m2に達した。 東京大、高伝導性オリゴマー型有機伝導体を開発

東京大、高伝導性オリゴマー型有機伝導体を開発

東京大学は、導電性高分子をモデルとして、室温以上で金属化する新たな「高伝導性オリゴマー型有機伝導体」を開発した。既存物質に比べ100万倍の伝導度を達成したという。 “肌触り”を計測し、美容ケアの効果を可視化

“肌触り”を計測し、美容ケアの効果を可視化

触覚センサーの開発/提供を行うタッチエンスは、「電子機器トータルソリューション展2023」(2023年5月31日〜6月2日)に出展し、指先から全身までの触覚情報を可視化するセンサー「ショッカク」シリーズを展示した。 京都大、室温で高温超伝導モーターの運転に成功

京都大、室温で高温超伝導モーターの運転に成功

京都大学は、高温超伝導誘導同期モーター(HTS-ISM)の室温運転に成功した。同モーターの巻き線を「高温超伝導体」と「常伝導体」のハイブリッド構造としたことで、仮に超伝導状態を維持できなくなっても、焼損などのリスクを回避し連続運転が可能となる。 NIMSら、リチウム空気電池の劣化反応機構を解明

NIMSら、リチウム空気電池の劣化反応機構を解明

物質・材料研究機構(NIMS)は、ソフトバンクやオハラと共同で、リチウム空気電池の劣化反応機構を解明した。これに基づき、金属リチウム負極の劣化を抑えるための軽量な保護膜を導入し、サイクル寿命を大幅に向上させることに成功した。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- 「世界2位」は実現するか、ローム、東芝、三菱電機とデンソーの選択は

- Musk氏は「半導体製造の再定義」を目指すのか

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- ローム、8インチSiC MOSFET開発の技術目標を2年前倒しで達成

- 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円

- シャープ新社長は海外事業出身 鴻海と連携で「新たな成長ステージへ」

- 米Waymoの世界展開は東京から 「開始まで何年もかからない」