Armがチップレットで本領発揮へ エコシステム構築を加速:「NVIDIA代替」も目標に(2/3 ページ)

UCIeも3Dパッケージングをサポート

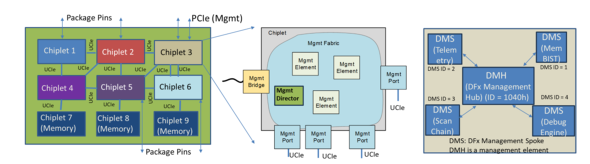

UCIeコンソーシアムは2024年8月に、2.0仕様をリリースした。このアップデートにより、複数のチップレット全体のSiPライフサイクルのための試験性や管理の容易性、デバッグを考慮した設計(DFx)などの設計上の課題に対応する。このアップデートの重要な特徴は、チップレットの帯域幅密度と電力効率を劇的に高められる3Dパッケージングをサポートしているという点だ。

UCIe 2.0仕様におけるUCIe-3Dは、バンプピッチが10〜25ミクロンから1ミクロン未満のハイブリッドボンディングに向けて最適化されている[クリックで拡大] 出所:UCIe Consortium

UCIe 2.0仕様におけるUCIe-3Dは、バンプピッチが10〜25ミクロンから1ミクロン未満のハイブリッドボンディングに向けて最適化されている[クリックで拡大] 出所:UCIe ConsortiumRamirez氏は、「Armは、Intel Foundry ServicesやSamsung Electronics、TSMCとの協業により、チップテストやPoC(概念実証:Proof of Concept)、さらには完全な製品のためのプログラムを開発している。現在、このようなプロジェクトを手掛ける設計パートナーやASIC設計パートナー、機器メーカーが15社ほど存在する」と述べる。

また同氏は、「最後の鍵となるのは、CadenceやAlphawaveのような、UCIeインタフェースをベースとしたチップレットの接続をサポートしているサードパーティーIPベンダーだ。われわれは現在、こうした企業との連携により、ロードマップの調整を進めている」と付け加えた。

「Arm Total Designは、『Grace Hopper』やその他のNVIDIAベースのGPUソリューションの代替を提供するという目標などもあり、大きな注目を集めているプロジェクトだ。最近発表されたチップレットプラットフォームでは、韓国のパートナーであるADTechnologyが、Armのコンピュートサブシステムを使用して64コアのコンピュートチップレットを開発している。同社はこれを、RebellionのAIアクセラレーターとSamsungのHBMメモリと組み合わせて、1つのパッケージ製品にする予定だ」(Ramirez氏)

また同氏は、「この製品は、NVIDIAが現在提供しているソリューションよりも3倍高い電力効率と性能を達成し、複雑なチップレット統合を実現可能であることを実証するだろう」と付け加えた。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待