2025年は数年に一度の「ビッグチェンジ」イヤー、NVIDIAとAMDの最新GPUを分解:この10年で起こったこと、次の10年で起こること(94)(3/4 ページ)

4つのシリコンを比較する

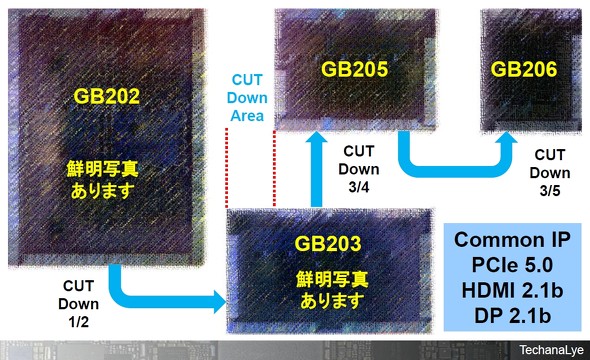

図5はエントリーのRTX 5050 GB207を除くNVIDIA Blackwellの4シリコンの様子である。カットダウンで構成されるスケーラブルシリコンになっている。演算器コア数やキャッシュメモリとともに、VRAMインタフェースのチャンネル数もカットダウンされている。個々のコア、PHYは同じものを活用し、スケールの変更でバージョンを作り上げているわけだ。スケール化することでテストパターンなどが流用できる利点なども大きい。一番大きなシリコンであるRTX 5090 GB202が設計難易度は一番高い。搭載トランジスタが多く、電源ドロップ、ノイズ対策、クロックスキュー調整などの課題は面積に比例して増える。一番難易度の高いものを先に設計して、それをベースにしてカットダウンすることがもっとも合理的だ(一般的に大きいチップほど電源ドロップも大きく、クロックスキュー合わせなどが難しいので製品周波数も大きいチップが若干低い)。

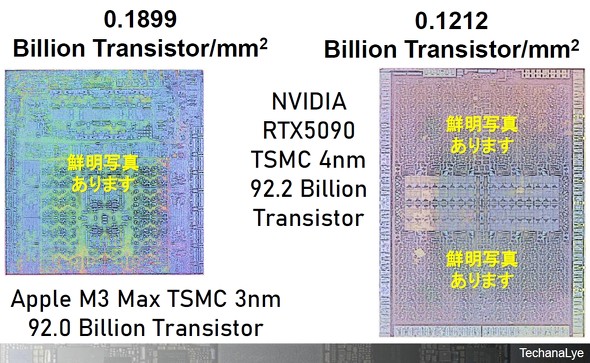

図6は現在市販される最大トランジスタ搭載チップ2件の様子である。ともに920億トランジスタ超え。製造プロセスが異なるので同軸比較にはならないが、ともに1平方ミリメートル当たり1億トランジスタを超えている。スマートフォン向けでは、既に1平方ミリメートル当たり2億トランジスタ超えチップも出回っており、今後2nm世代、1.4nm世代のプロセスなどで3億超えを見る日も近いだろう。

25年前のチップと比較してみる

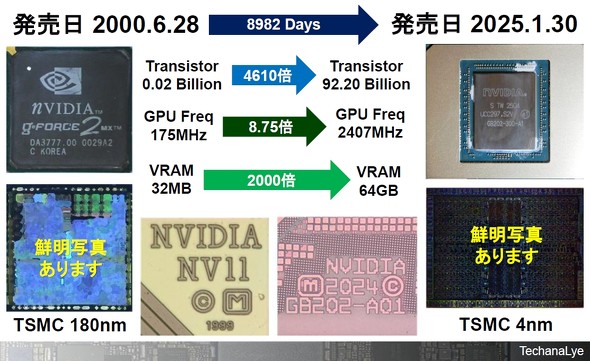

図7は25年前のNVIDIA「NV11(開発コードネーム)」と最新のRTX 5090の比較である。さまざまな数字が数千倍となっている。四半世紀の進化が目に見える数字となっているわけだ(あらためて感慨深い!)。今後もややペースは落ちるもののイノベーテッドな数字を見続けることができそうなので、日々努力を重ねている製造や設計開発メーカー、エンジニアに敬意を示したい。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング