ボイドフリーで成膜可能、先端パッケージング用PECVD装置:膜厚は最大100μm

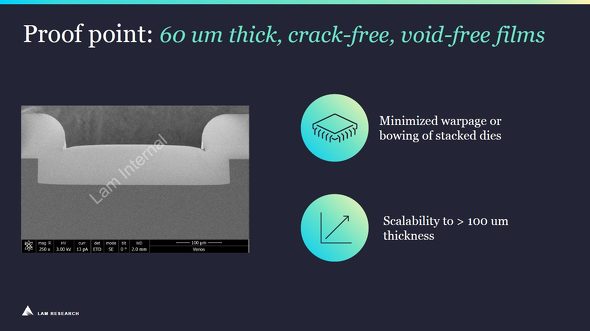

ラムリサーチは2025年10月に開催した記者説明会で、新しいプラズマ化学蒸着(PECVD)装置「VECTOR TEOS 3D」について説明した。先端パッケージング向けの装置で、反りが大きいウエハーにも厚さ60μm以上の絶縁体膜を成膜できる。これにより、ダイ間埋め込みの工程において、ボイドやクラックのない絶縁体膜を作成できるとする。

Lam Researchは2025年9月、先端パッケージ向けに、60μm以上の膜厚で成膜できるプラズマ化学蒸着(PECVD)装置「VECTOR TEOS 3D」を発売した。チップ/ダイの3次元(3D)積層や、チップレット集積などのヘテロジニアスインテグレーションに向け、ボイドやクラックのないダイ間ギャップフィルの成膜が可能になる。

Lam Researchの日本法人ラムリサーチでリージョナル・プロセステクノロジーグループ・シニアディレクターを務める中村健嗣氏は、2025年10月23日に開催された記者説明会で「先端パッケージで生じる新たな課題に対応する装置」だと強調した。

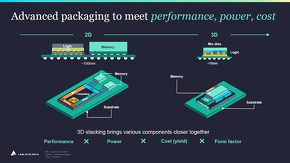

3D-ICやヘテロジニアスインテグレーションなどに代表される先端パッケージング技術は、AI半導体のさらなる高性能化に不可欠とされる。CPUとメモリの距離が近づき、処理速度の向上を実現できるものの、製造時に新たな課題も生まれている。チップを垂直方向に積層するので、プロセス中に生じる膜応力により、ウエハーに反りやゆがみが発生することだ。これにより、膜にひび割れやボイドが発生し、欠陥や歩留まり低下といった問題につながる。中村氏は「3D NAND型フラッシュメモリでも、DRAMを積層する広帯域メモリ(HBM)でも、3D積層技術を用いる半導体では、これが共通の課題になっている」と説明する。

VECTOR TEOS 3Dは、ダイ間の埋め込み(ギャップフィル)工程に特化した最大60μm厚の絶縁体膜を、ナノスケールの精度で成膜できることが特徴だ。膜厚は100μmまで厚くできるという。「現時点では60〜100μmの膜厚があれば、高品質なギャップフィルが可能になると考えている」(中村氏)。さらに、独自のクランピング技術を適用することで、大きく反ったウエハーに対しても均一に成膜できる。これらの技術により、クラックやボイドのない絶縁膜を作ることが可能になる。

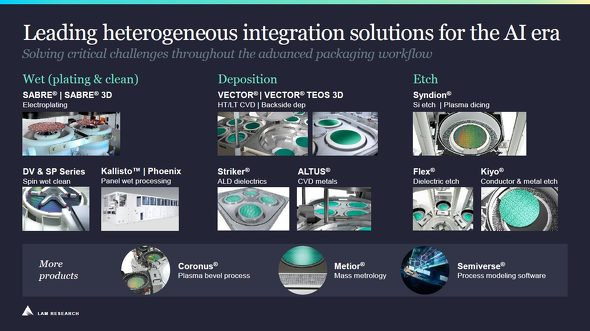

VECTOR TEOS 3Dは、Lam ResearchのPECVD装置「VECTOR」シリーズの1種で、他のVECTORシリーズと同じプラットフォームをベースにしている。4つのステーションを備えていて並列処理ができるので、プロセスタイムを低減できる。VECTOR TEOS 3Dは、同社の従来装置である「VECTOR TEOS」に比べ、スループットを約70%向上させた。コストオブオーナーシップも最大20%改善できるとする。

VECTOR TEOS 3Dは、先端ロジックと先端メモリの工場で既に導入されている。「1年以上の量産実績があり、その上で、絶縁体膜のボイドフリーやクラックフリーを達成できている」(中村氏)

中村氏は「Lam Researchは半導体製造前工程向けの装置を手掛ける印象が強いかもしれないが、後工程向けでも多くの装置をそろえている」と続ける。銅めっき成膜装置「SABRE」シリーズや、深いシリコン貫通ビア(TSV)を加工できるエッチング装置「Syndion」シリーズなどだ。

中村氏は、半導体業界がAIによって転換点を迎えていると述べる。メモリウォール問題(CPUの進化により、メモリへのアクセス速度が相対的に遅くなり、演算のボトルネックとなる問題)、消費電力と発熱、性能とコストの両立といった課題が、以前よりも顕著になり、これらを解決する手段の一つとして、先端パッケージングへの注目度が高まっているからだ。同氏は「AIの普及を加速させるためには、従来とは異なるアプローチが必要になる」と強調し、VECTOR TEOS 3Dはそうしたアプローチをサポートすると語った。

関連記事

配線工程もいよいよ次世代へ ラムリサーチのモリブデン対応ALD装置

配線工程もいよいよ次世代へ ラムリサーチのモリブデン対応ALD装置

ラムリサーチは、配線工程において、従来のタングステンに代わり、モリブデンを使用する原子層堆積(ALD)装置を発表した。次世代のロジックやメモリの製造に向け、より低抵抗の金属で配線を形成できるようになる。併せて、新たなプラズマ制御機構を用いたエッチング装置も発表した。 「超垂直な」メモリホールを高速加工 1000層NANDの実現に向け

「超垂直な」メモリホールを高速加工 1000層NANDの実現に向け

Lam Researchは、1000層を超える3D(3次元) NANDフラッシュメモリの加工に向け、極低温絶縁膜エッチング技術の最新世代「Cryo 3.0」を発表した。100:1という高いアスペクト比のメモリホールを、極めて垂直に高速で加工できるという。 HARエッチングとナノスケールパターニングで実現するメモリロードマップ

HARエッチングとナノスケールパターニングで実現するメモリロードマップ

メモリ技術は市場の要求に応じて、より高密度かつ高性能、そして新素材や3D構造、高アスペクト比(HAR)エッチング、EUV(極端紫外線)リソグラフィへと向かっている。本稿では、これらの方向性を見据えた、Lam Researchの開発内容を紹介する。 HBM系が主役、DDR系が脇役になるDRAM市場

HBM系が主役、DDR系が脇役になるDRAM市場

今回から、2025年8月に開催された「FMS(the Future of Memory and Storage)」の一般講演の一つを紹介する。アナリストであるJim Handy氏の講演「Memory and Storage, Current Status and Future Projections(メモリとストレージの現状と将来)」だ。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- 次世代パワー半導体 「期待の5材料」の現在地

- パワー半導体世界市場、2035年は7兆円超え 酸化ガリウムも一定規模に

- 入学した瞬間終わったわ――「講義が英語」なんて一言も聞いてない!

- TED、25年度は減収減益 「各事業磨き上げる」と新社長

- SK hynixの四半期決算、驚異の売上高営業利益率70%超え

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

ラムリサーチ 中村健嗣氏

ラムリサーチ 中村健嗣氏