AI/HPCの性能を左右する電源供給網の安定化(前編):福田昭のデバイス通信(514) TSMCが解説する最新のパッケージング技術(11)(2/2 ページ)

電源のインピーダンスは高周波領域で急激に上昇

理想的な電源は、常に一定の電圧を全ての半導体チップに供給する。実際には、このようなことはあり得ない。負荷の変動に対してわずかに遅れて電流の供給量を制御しており、供給電流の変化によって電源電圧は常に変動している。

電源電圧の変動は主に、電源電流の時間的な変動によって生じる。負荷が変動するサイクル(周波数)はクロックサイクル(クロック周波数)と、論理回路やメモリ回路などのスイッチングサイクル(スイッチング周波数)および、これらの高調波の重なりとなる。

電源インピーダンスの値は周波数の上昇とともに急速に高まる。そして共振点(最大インピーダンスあるいはピーク値)を過ぎると、周波数の上昇とともにインピーダンスは低下する。電源インピーダンスのピーク値は、なるべく低くすることが望ましい。

何も対策しない電源供給網の電源インピーダンスは例えば、10kHzを基準にすると1MHzではおよそ10倍、数十MHzではおよそ100倍に達する。

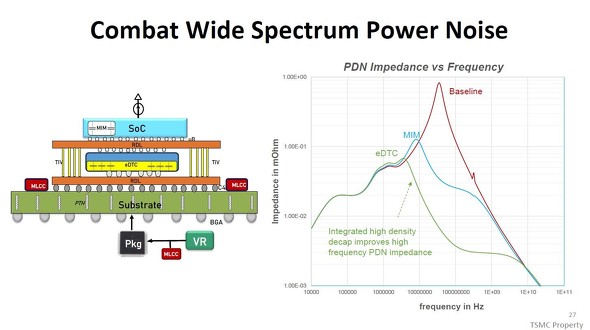

CoWoS-Lタイプの先進パッケージにおける電源インピーダンスの低減。左はパッケージの構造図。右は電源供給網(PDN)のインピーダンス(縦軸)と周波数(横軸)の関係。ベースライン(赤色)は通常の特性。MIM(水色)とeDTC(黄緑色)はキャパシターの挿入によるインピーダンス低減策を講じた特性[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

CoWoS-Lタイプの先進パッケージにおける電源インピーダンスの低減。左はパッケージの構造図。右は電源供給網(PDN)のインピーダンス(縦軸)と周波数(横軸)の関係。ベースライン(赤色)は通常の特性。MIM(水色)とeDTC(黄緑色)はキャパシターの挿入によるインピーダンス低減策を講じた特性[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)高周波インピーダンスを下げるためには通常、キャパシターあるいはコンデンサーが使われる。CoWoS-Lタイプの先進パッケージでは、SoC(System on a Chip)チップの内部にMIM(Metal-Insulator-Metal)キャパシター群を作り込んだり、LSI(Local Silicon Interconnect)チップの内部にeDTC(embedded Deep Trench Capacitor)群を作り込んだりする。

MIMキャパシター群を組み込んだ電源供給系の最大インピーダンスは対策前の約6分の1に、eDTC群を作り込んだ電源供給系の最大インピーダンスは対策前の約10分の1に減少する。またキャパシターによるインピーダンスの低減効果はピーク周波数よりも高い領域で大きい。10MHz〜100MHzの領域では、対策前と比べてMIMキャパシターでは約10分の1、eDTCでは約100分の1とインピーダンスが大幅に小さくなる。

(後編に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

ネットワークの大規模化と高速化が電気から光への転換を促す

ネットワークの大規模化と高速化が電気から光への転換を促す

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。今回は、「(4)Energy efficient of scale-up networking(ネットワークの大規模化おける消費エネルギー(転送データ当たり)の効率)」を取り上げる。 AI/HPCシステムの死命を制する消費電力・放熱設計(後編)

AI/HPCシステムの死命を制する消費電力・放熱設計(後編)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。前編に続き、「(3)Thermal dissipation design(消費電力および放熱の設計)」の内容を解説する。 AI/HPCシステムの死命を制する消費電力・放熱設計(前編)

AI/HPCシステムの死命を制する消費電力・放熱設計(前編)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。「(3)Thermal dissipation design(消費電力および放熱の設計)」を前後編に分けて解説する。 世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

世界半導体市場は26年2月に大幅成長、日本のみ9カ月連続マイナスに

米国半導体工業会によると、2026年2月の世界半導体売上高は前年同月比61.8%増の888億米ドルと大幅な増加を記録したという。ただ、地域別では日本のみマイナス成長となっている。日本が前年同月比減となるのは9カ月連続だ。 Micronの四半期業績、利益額と利益率がともに過去最高を更新

Micronの四半期業績、利益額と利益率がともに過去最高を更新

今回は、Micron Technologyの2026会計年度第2四半期(2025年12月〜2026年2月期)の四半期業績を紹介する。 ミニダイ(チップレット)間接続におけるSTCO

ミニダイ(チップレット)間接続におけるSTCO

「IEDM 2025」におけるTSMCの講演内容を紹介する。前回に続き、アウトラインの第3項「System-Technology Co-Optimization (STCO)(システム・製造協調最適化)」の内容を解説する。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング