シリコンフォトニクスと先進パッケージの統合が描く未来:福田昭のデバイス通信(516) TSMCが解説する最新のパッケージング技術(13)(2/2 ページ)

先進パッケージの内部にシリコンフォトニクスを埋め込む

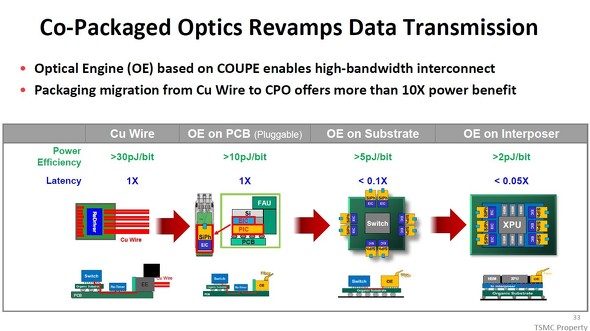

PICとEIC、光ファイバ結合器で構成したモジュールをTSMCは「OE(Optical Engine)」と呼んでいる。OEの実装形態はいくつか存在する。最も簡素なのは、ボード(プリント回路基板)にOEを搭載することだ。これだけで銅ケーブル(Cu wire cable)接続に比べ、1ビット当たりの転送に必要なエネルギーを約3分の1(10pJ/ビット)に減らせる。

パッケージ基板に高速スイッチICと複数のOEを混載したのが、進化形態である。1ビット当たりの転送エネルギーは5pJ/ビットと進化前の半分に減り、遅延時間(レイテンシ)は進化前の10分の1と大幅に短くなる。

COUPE(クーペ)をベースとした光エンジン(OE)の実装形態と転送エネルギー、遅延時間(レイテンシ)の比較。左端は光エンジンを使わない、従来の銅線接続[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

COUPE(クーペ)をベースとした光エンジン(OE)の実装形態と転送エネルギー、遅延時間(レイテンシ)の比較。左端は光エンジンを使わない、従来の銅線接続[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)さらに進化させた形態では、先進パッケージ技術の中間基板(インターポーザ)にOEを混載する。大規模プロセッサ(XPU)とOEをインターポーザ経由で接続することにより、転送エネルギーと遅延時間(レイテンシ)がさらに減る、あるいは短くなる。ビット当たりの転送エネルギーは2pJ/ビット、レイテンシは進化前(ボードにOEを搭載)の20分の1になるとする。

光変調の高速化、コパッケージ化、FAU増強

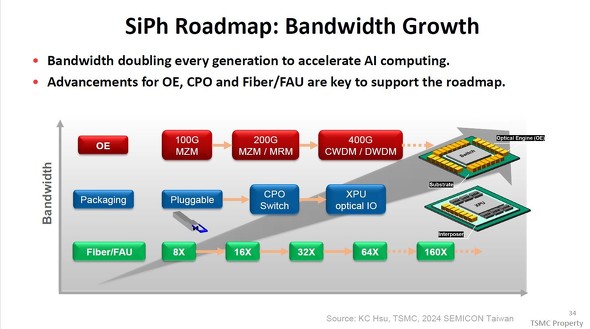

光エンジン(OE)技術、パッケージング技術、FAU技術の改良により、シリコンフォトニクスが扱う帯域幅は世代ごとに倍増してきた。具体的には100Gビット/秒の世代、次が200Gビット/秒の世代、その次が400Gビット/秒の世代へと進化した。この進化に直接関わるのは光エンジン技術、具体的には光変調技術の高速化と波長分割による多チャネル化だ。

光変調器にはマッハツェンダー変調器(MZM:Mach-Zender Modulator)やマイクロリング変調器(MRM:Micro Ring Resonator Modulator)などが使われる。波長分割による多チャンネル化には、波長分割多重(WDM:Wavelength Division Multiplexing)方式が使われる。WDMには波長間隔の広い粗密度WDM(CWDM:Coarse WDM)と波長間隔の狭い高密度WDM)(DWDM:Dense WDM)がある。

シリコンフォトニクス技術のロードマップ。縦軸は要素技術(光エンジン(OE)、パッケージング、FAUのファイバ数)とデータ転送速度(矢印のイメージ)、横軸は時間[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

シリコンフォトニクス技術のロードマップ。縦軸は要素技術(光エンジン(OE)、パッケージング、FAUのファイバ数)とデータ転送速度(矢印のイメージ)、横軸は時間[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)パッケージング技術とFAU技術は、光変調技術の高速化に応じて改良される。パッケージング技術の改良については既に述べた。FAU技術ではユニットのファイバ数を8から16、32、64と倍増させることで帯域幅を高める。

(次回に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

関連記事

AI/HPCの性能を左右する電源供給網の安定化(前編)

AI/HPCの性能を左右する電源供給網の安定化(前編)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。今回は5番目の項目「(5)Power delivery efficiency(電源供給の効率)」を前後編の2回に分けて解説する。 ネットワークの大規模化と高速化が電気から光への転換を促す

ネットワークの大規模化と高速化が電気から光への転換を促す

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。今回は、「(4)Energy efficient of scale-up networking(ネットワークの大規模化おける消費エネルギー(転送データ当たり)の効率)」を取り上げる。 AI/HPCシステムの死命を制する消費電力・放熱設計(後編)

AI/HPCシステムの死命を制する消費電力・放熱設計(後編)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。前編に続き、「(3)Thermal dissipation design(消費電力および放熱の設計)」の内容を解説する。 AI/HPCシステムの死命を制する消費電力・放熱設計(前編)

AI/HPCシステムの死命を制する消費電力・放熱設計(前編)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。「(3)Thermal dissipation design(消費電力および放熱の設計)」を前後編に分けて解説する。 Micronの四半期業績、利益額と利益率がともに過去最高を更新

Micronの四半期業績、利益額と利益率がともに過去最高を更新

今回は、Micron Technologyの2026会計年度第2四半期(2025年12月〜2026年2月期)の四半期業績を紹介する。 560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

560億ドル投資でも「需要に追い付けない」 AI急成長でTSMC表明

TSMCの2026年の設備投資額は560億米ドルに達する見込みだ。それでも、AI半導体の旺盛な需要に応えるには不十分だという。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング