シリコンフォトニクスと先進パッケージの統合が描く未来:福田昭のデバイス通信(516) TSMCが解説する最新のパッケージング技術(13)(1/2 ページ)

「IEDM 2025」におけるTSMCの講演内容を紹介するシリーズ。今回からは、次世代の先進パッケージ技術に関する内容を解説する。

第4項「次世代の先進パッケージ技術」の説明を開始

2025年12月に開催された国際学会IEDMのショートコース(技術解説)で、シリコンファウンドリー最大手のTSMCが最新のパッケージング技術を説明した。講演のタイトルは「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」、講演者はAdvanced Package Integration Division R&DのディレクターをつとめるJames Chen氏である。大変に参考となる内容だったので、その一部をシリーズでご紹介している。ただし講演内容だけでは説明が不十分なところがあるので、本シリーズでは読者の理解を助けるために、講演内容を筆者が適宜、補足してある。あらかじめご了承されたい。

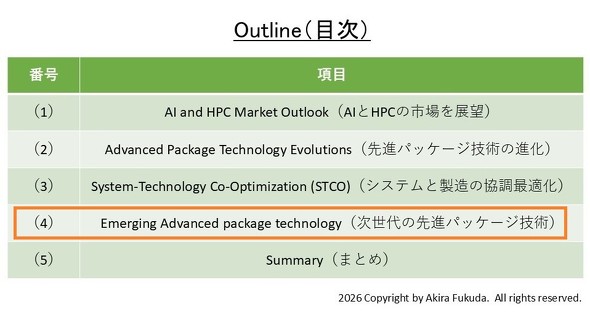

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)

講演「Advanced Packaging and Chiplet Technologies for AI and HPC Applications(AIおよびHPCに向けた先端パッケージング技術と先端チップレット技術)」のアウトライン[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)タイトルスライドの次に示されたアウトラインは、「AI and HPC Market Outlook(AIとHPCの市場を展望)」「Advanced Package Technology Evolutions(先進パッケージ技術の進化)」「System-Technology Co-Optimization (STCO)(システムと製造の協調最適化)」「Emerging Advanced package technology(次世代の先進パッケージ技術)」「Summary(まとめ)」となっていた。

本シリーズの第5回からは、アウトラインの第3項「System-Technology Co-Optimization (STCO)(システム・製造協調最適化)」に相当する部分の説明に入った。先進パッケージ「CoWoS-L(LSI+RDL interposer)」を例に、STCOで考慮すべき5つの項目を順に説明してきた。前回で第3項に関するご報告は完了した。今回からは第4項、「Emerging Advanced package technology(次世代の先進パッケージ技術)」に関する内容をご報告する。

シリコンフォトニクスを構成する2種類の回路ダイを積層

次世代の先進パッケージ技術としては最初に「シリコンフォトニクス」(シリコンベースの光伝送技術)を紹介した。TSMCは「COUPE(COmpact Universal Photonic Engine)」と名付けたシリコンフォトニクス技術を開発してきた。なお「COUPE(クーペ)」の基本概念については本コラムで過去に解説しているので、ご興味のある方は参照されたい。

本ショートコースでは、先進パッケージ技術(SoIC技術)を駆使したCOUPEの概要を説明していた。数多くの光回路(PIC:Photonic Integrated Circuit)を作り込んだウエハーに電気回路(EIC:Electronic Integrated Circuit)のダイを搭載してPICとEICを電気的かつ機械的に接続する。PICとファイバアレイユニット(FAU:Fiber Array Unit)は、回折格子型結合器(GC:Grating Coupler)あるいはエッジ型結合器(EC:Edge Coupler)を介して光接続する。なおGCとECについても本コラムで過去に解説している(「シリコンフォトニクス技術「COUPE」が導波路とファイバを高い効率で結ぶ」)ので、ご興味のある方は参照されたい。

Copyright © ITmedia, Inc. All Rights Reserved.

![先進パッケージ技術(ウエハーとダイの積層技術)を導入した「COUPE(クーペ)」の製造工程(概要のみ)[クリックで拡大] 出所:TSMC(IEDM 2025のショートコース(番号SC1-5)で公表された講演スライドから)](https://image.itmedia.co.jp/ee/articles/2604/24/mm260424_device02.jpg)