ボードの電源系雑音、最適設計で解決:実装技術 パワーインテグリティ(3/3 ページ)

【寄稿】電源分配の最適化技術を開発、最小コストで高い品質を実現

当社(米Sigrity社)は、部品を搭載したプリント配線基板(ボード)における電源分配回路の品質(パワー・インテグリティ)を、製造コストを考慮しながら自動的に最適化する技術を開発した。この技術に基づく自動最適化ソフトウエア「OptimizePI」を製品化し、すでに出荷を始めている*3)。

電源品質と製造コストを指標として、電源分配回路を構成するデカップリング・コンデンサの品種や搭載位置を最適化する。電源品質の確保とコストの最小化を同時にこなすこうしたEDAツールの製品化は、業界で初めてだ。電源品質とコストは次元が異なる要素であり、これまでは、パワー・インテグリティに習熟した技術者が電源分配回路の解析に向けた最新のEDAツールを駆使しても、両立は難しかった。

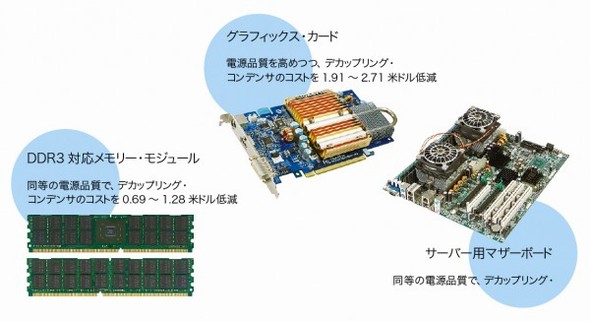

この最適化ツールをすでに導入した複数のユーザーからの報告によれば、電源品質を確保しながら、電源分配回路の製造コストを15〜50%も削減できた(図1)。ボード1枚当たり数米ドルのコスト削減に相当する。大量生産するボードであれば、削減効果は極めて大きな金額になる。

図1 品質そのままにコストを15〜50%削減 開発したツール「OptimizePI」を使って電源分配回路を最適化したボードの事例である。DDR3対応のメモリー・モジュールは、電源品質を維持しながら、電源分配回路の製造コストを0.69米ドル削減するとともに、デカップリング・コンデンサの実装面積を32%削減できた。1000個を超えるデカップリング・コンデンサを搭載した高性能サーバー・ボードでも、電源品質を確保しながら、電源分配回路の製造コストを30%削減できた。

図1 品質そのままにコストを15〜50%削減 開発したツール「OptimizePI」を使って電源分配回路を最適化したボードの事例である。DDR3対応のメモリー・モジュールは、電源品質を維持しながら、電源分配回路の製造コストを0.69米ドル削減するとともに、デカップリング・コンデンサの実装面積を32%削減できた。1000個を超えるデカップリング・コンデンサを搭載した高性能サーバー・ボードでも、電源品質を確保しながら、電源分配回路の製造コストを30%削減できた。第2部ではまず、こうした最適化ツールを開発した背景と、電源分配回路の現在の設計フローが抱える課題を解説する。続いて、新たに開発した最適化技術に基づく設計フローを具体的に説明する。また最後に、このツールを利用して電源分配回路を設計した事例を紹介する。

なお、開発した最適化技術は、ボード自体の電源分配回路のみならず、ボードに搭載する半導体ICのパッケージ内部の電源分配回路も同時に最適化することが可能だ。ただし一般にボードの方が、ICパッケージに比べて電源分配回路を構成する部品点数が多い。従ってボードの方が、今回のツールで電源品質を高めたりコストを削減したりできる可能性が高い。

電源分配のコストが急増

この最適化ツールを開発した動機は、ボードの電源分配回路に費やされる製造コストが急増していることにある。背景にあるのは、デジタルLSIに向けた半導体プロセス技術の微細化だ。後で詳しく説明するが、微細化とともにボードの電源品質を確保することが難しくなり、対策部品の使用個数が増えているのである。使用個数が増えれば、部品コストのみならず、プリント配線基板の加工や部品の実装に必要なコストも増加してしまう。

もう少し詳しく、順番に説明しよう。まず、半導体プロセス技術の微細化によって電源品質の確保が難しくなる理由は次の通りだ。

微細化が進展した結果、デジタルLSIの電源電圧は1Vを下回るまでに低下した。このため、電源に重畳する雑音に対する許容度(マージン)は減少している。その一方で、LSIが引き込む電流は、静的な電流も動的な電流も増加する傾向にある。LSIの外部インターフェースの伝送速度が高まるとともに、信号線の本数も増えているからである。さらに、内部論理回路の大規模化と高速化が拍車を掛ける。この結果、振幅が50Aを超えるスイッチング電流が過渡的に生じることも、今や珍しくない。

ここで、電源分配回路に生じる雑音電圧の大きさ(ΔV)は一般に、電源プレーンのインピーダンス(Z)にスイッチング電流の振幅(ΔI)を乗じた値に比例する。つまり次式で表せる。

ΔV 〜 Z × ΔI ――(1)

すなわち、スイッチング電流が増加すると雑音電圧は大きくなってしまうわけだ。

さらに、消費電力やスイッチング電流の振幅が大きい、複数個のデジタルLSIが1枚のボードに搭載されることも、電源品質の確保を難しくしている要因だ。例えばプロセッサとASIC、FPGAをすべて搭載したボードである。こうしたボードでは、スイッチング電流の振幅がさらに大きくなる可能性がある。

目標インピーダンスは激減

次に、電源品質を確保する対策部品の使用点数が増えている理由を説明する。

(1)式から分かるように、スイッチング電流が増加しても雑音電圧を低く抑えるためには、LSIから見た電源分配回路のインピーダンスを低減しなければならない。それでは一体、どの程度まで低減すればよいのだろうか。この指標がいわゆるターゲット・インピーダンス(Ztarget)である。この算出にはさまざまな手法が提案されているが、簡易的にはLSIへの供給電圧(V)に対する最大許容雑音電圧(ΔV)とスイッチング電流の振幅(ΔI)から、次式で求められる。

Ztarget = ΔV / ΔI = (V × 5%) / ΔI ――(2)

ここで5%という値は、一般的なデジタルLSIが供給電圧に許容する最大電圧誤差である。

ターゲット・インピーダンスの値は、以前に比べて大幅に低くなっている。1980年代の終盤には、デジタルLSIの電源電圧は5Vが一般的で、スイッチング電流の振幅は1A程度にとどまっていた。(2)式に当てはめるとターゲット・インピーダンスは250mΩと求められる。

ところが現在では、前述の通り1V、50Aに達した。ターゲット・インピーダンスはわずかに1mΩである。実に2けた以上も低くなっているのだ。このため電源分配回路のインピーダンスを低減するデカップリング・コンデンサの使用個数が増えてしまうのである。

複数品種使って広帯域化

電源分配回路のインピーダンスを広い帯域にわたって低く抑えるためには、複数のデカップリング・コンデンサをうまく組み合わせる必要がある。この点について詳しく説明しよう。

ボードには、LSIに供給する電源電圧を安定化するDC-DCコンバータ回路を搭載する。この回路の出力に取り付けた大容量コンデンサ(いわゆるバルク・コンデンサ)は、品種によって違いはあるが、直流(DC)から10kHz、あるいは100kHzの周波数領域にわたってインピーダンスを低く維持できる。

これを超える周波数領域では、ボードに搭載したデカップリング・コンデンサが電源分配回路のインピーダンスを低く抑える役割を担う。

バルク・コンデンサとデカップリング・コンデンサは、振る舞いが大きく異なる。バルク・コンデンサは、DC-DCコンバータ回路の過渡的なスイッチング電流に対する電荷を貯蔵することで、出力電圧を平滑化する役割を果たす。一方のデカップリング・コンデンサは、直列RLC共振回路を形成し、電源層とグラウンド(接地)層の間に低インピーダンスのパス(経路)を形成する。

このRLC共振回路の構成要素である静電容量(C)は、デカップリング・コンデンサ自体の静電容量に、電源/グラウンド層が形成した平行平板導体の静電容量を足した値になる。

インダクタンス(L)は、デカップリング・コンデンサのESL(等価直列インダクタンス)と、LSIから電源分配回路を見たときの寄生インダクタンスの合計である。なおこの寄生インダクタンスは、電源/グラウンド層そのものと、デカップリング・コンデンサの搭載用パッド、層間を接続するビア・ホールをつないだ電流ループのインダクタンス(ループ・インダクタンス)に相当する。

抵抗(R)は、デカップリング・コンデンサのESR(直列等価抵抗)と、電源/グラウンド層の抵抗損失を足し合わせた値になる。

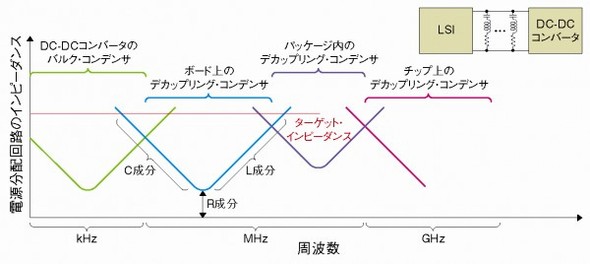

ここで電源品質の最適設計とは、可能な限り広い周波数帯域にわたって、電源分配回路のインピーダンスをなるべく低く抑えることである。そのためには、電源分配回路内のRLC共振回路は、広帯域の共振周波数特性を備えていなければならない。これを達成する現実的な手段は、デカップリング・コンデンサの品種と搭載位置を最適化することである(図2)。ループ・インダクタンスに比べて、ボード設計者が大幅に広い範囲で値を調整できるからだ。

図2 コンデンサごとに担当領域が異なる 一般に電源分配回路では、品種の異なるコンデンサを組み合わせて広帯域/低インピーダンスを実現する。電源分配回路は各周波数において、コンデンサと電源/グラウンド層の静電容量(C)成分とインダクタンス(L)成分、抵抗(R)成分からなる直列RLC共振回路として振る舞う。この特性に注意して、LSIから見たインピーダンスを目標値以下に抑える。

図2 コンデンサごとに担当領域が異なる 一般に電源分配回路では、品種の異なるコンデンサを組み合わせて広帯域/低インピーダンスを実現する。電源分配回路は各周波数において、コンデンサと電源/グラウンド層の静電容量(C)成分とインダクタンス(L)成分、抵抗(R)成分からなる直列RLC共振回路として振る舞う。この特性に注意して、LSIから見たインピーダンスを目標値以下に抑える。ボード上に搭載するデカップリング・コンデンサには、通常、静電容量が1n〜100μFの品種を使う。このコンデンサによってインピーダンスの目標値を達成できる周波数の上限は、デカップリング・コンデンサの静電容量の最小値とループ・インダクタンスの最小値によって決まり、10M〜100MHzの範囲である。

ボード上のデカップリング・コンデンサが機能する上限周波数を上回る領域では、ICパッケージに内蔵したデカップリング・コンデンサが電源分配回路のインピーダンスを抑える役割を担う。パッケージ内のデカップリング・コンデンサも、動作原理はボード上のデカップリング・コンデンサとまったく同じだ。つまり直列RLC共振回路を構成し、スイッチング電流に対して電源-グラウンド間の低インピーダンス・パスを形成する。

パッケージに内蔵するデカップリング・コンデンサの静電容量は通常、1n〜10μFである。ループ・インダクタンスは、ボード上のデカップリング・コンデンサに比べると若干小さい。従ってパッケージ内のデカップリング・コンデンサは、最大400MHz程度までコンデンサとして機能する。ただし、デカップリング・コンデンサを内蔵したICパッケージは、製造コストが高くなるという問題があるため、注意してほしい。

この周波数を超える領域で電源分配回路のインピーダンスを低く抑えるには、半導体チップ上にデカップリング・コンデンサを集積する必要がある。デカップリング・コンデンサとしての動作原理はボードやICパッケージに搭載するデカップリング・コンデンサと同じだが、トランジスタのゲート容量を利用するなど、実現手法は異なっている。

ここまで説明した通り、電源のインピーダンスを広い帯域にわたって低く抑える作業は、ボードのみならず、ICパッケージや半導体チップの設計も巻き込む複雑な仕事である。ただし通常、ボードの設計者は、パッケージやチップの電源分配回路を自ら設計するわけではない。従って、ボードに搭載するLSIが求めるターゲット・インピーダンスを厳密には知り得ないのである。半導体ベンダーがターゲット・インピーダンスの情報を提供していない場合は、前述の(2)式を使って簡易的に求められる。

現行の手法が抱える課題

それでは次に、ボードにおける電源分配回路の設計手法が現在抱えている課題について解説しよう。

当社をはじめとするEDAベンダー各社は、電源分配回路の電気的な特性を詳細に解析するツールを提供中である*4)。ところが実際にこうしたツールを使いこなしているのは、パワー・インテグリティを専門とする技術者に限られる。パワー・インテグリティを専門としない技術者や、そもそも電源品質にそれほど気を配る必要がないボードを扱う設計者は、経験則に頼って電源分配回路を設計しているのが実情だ。

例えば、「スイッチング電流の振幅が大きい電源端子のなるべく近くにデカップリング・コンデンサを配置せよ」という経験則である。実際には、「ボード上のすべてのLSIのすべての電源端子にデカップリング・コンデンサを配置せよ」といった設計ルールが運用されている。特に性能が高いLSIを搭載するボードでは、「LSIに近接した実装領域が空いていれば、どんな場所であれとにかく、デカップリング・コンデンサを配置せよ」と厳格化することが多い。

さらに高性能メモリー・モジュールなど、電源分配回路のインピーダンス特性が設計ごとに大きくばらつく傾向が強いボードでは、「ボード上のあらゆる場所にデカップリング・コンデンサを配置せよ」とする場合もある。

ところがこうした経験則に従うと、電源分配回路の設計は過剰になりがちだ。すなわち、実際には不要なデカップリング・コンデンサがボード上に数多く搭載されることになってしまう。

パワー・インテグリティの専門家は、電源品質の低下というリスクを最小化すべく、過剰な品質の電源分配回路を設計してしまうことが多い。一方でパワー・インテグリティに習熟していない技術者は、経験則に沿って過剰な設計を施す上に、ターゲット・インピーダンスを所望の周波数帯域にわたって達成できないことがほとんどだ。

厄介な問題はこれだけではない。電源分配回路の設計には、電源品質と製造コストのトレードオフが数多く存在しており、その最適点を見つけ出すことが極めて難しいのである。

一例を挙げよう。デカップリング・コンデンサは通常、ループ・インダクタンスの最小化を狙って、LSIの電源端子のうち特に大きなスイッチング電流が流れる端子の近くに配置する。ところがこの場所はLSIに近接しており、LSIから数多くの信号線を引き出すために使われる貴重な領域である。従って電源品質の最適化に向けてデカップリング・コンデンサを電源端子に近接させれば、信号線を引き出しにくくなり、配線層の追加が必要になる可能性がある。

小型ボードの最適化を拡張

ただし小型のボードに限れば、すでにパワー・インテグリティを専門とする技術者は、既存の解析ツールを使って最適設計を実現している。解析ツールを使えば、電源分配回路のインピーダンスを広い周波数範囲にわたって簡単に求められるからだ。この情報を基に、ターゲット・インピーダンスを確保しながら、製造コストをなるべく低く抑えられるように、デカップリング・コンデンサの個数や品種、ボード上の搭載位置を手作業で最適化している。

しかし、比較的大型のボードでは、この手法は現実的ではない。対象は、数百個から数千個ものデカップリング・コンデンサを搭載するボードである。膨大な数のデカップリング・コンデンサの品種や搭載位置を手作業で最適化することは、実際には不可能だ。各デカップリング・コンデンサの搭載位置をなんらかの手法で解析的に決定した上で、すべての搭載位置において、数十品種のデカップリング・コンデンサそれぞれを実装した場合についてインピーダンス特性を解析しなければならないのだ。

こうした理由から、大型ボードで現在一般に採用されている設計手法は、あらかじめ詳細解析に向けたツールを使って設計ルールを開発しておき、ボード設計時にこの設計ルールを適用するというものだ。

そこで当社は、小型ボードにおいてパワー・インテグリティの専門家が手作業で実施している最適化手法を自動化し、大型ボードにも対応できるよう拡張したソフトウエア・ツールを開発した。これが今回のOptimizePIだ。このツールによって得られるメリットは、単に大型ボードの最適化が可能になることだけではない。パワー・インテグリティの専門家は最適化の作業をコンピュータに引き渡せるため、より重要な設計業務に時間を活用できるようになる。

電源分配回路の最適化に向けた専用のアルゴリズムを独自に開発することで実現した。電源分配回路の最適化では、デカップリング・コンデンサの品種や搭載位置が異なった、膨大な数の設計データを解析する必要がある。従って、一般的な最適化アルゴリズムは適用できなかった。

ユーザーの設計が出発点に

ここからは、開発した最適化ツールを使った電源分配回路の設計フローについて細かく説明していこう。このツールは、電源分配回路の2つの要素を自動的に最適化する機能を備える。すなわち、ボード上のさまざまな場所におけるデカップリング・コンデンサの搭載/非搭載と、各位置に搭載するデカップリング・コンデンサの品種である。

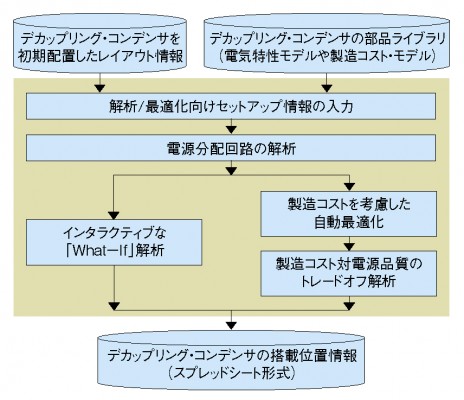

図3に、設計フロー全体の流れを示した。ユーザーが用意したボードの設計データとデカップリング・コンデンサの部品ライブラリを基に、電源分配回路の特性を解析し、製造コストをパラメータとして最適化を施す。

図3 初期設計を基にコンデンサ配置を最適化 OptimizePIによる最適化フローである。ユーザーによるボードの初期設計を基に、デカップリング・コンデンサの品種や搭載位置を変更しながらインピーダンス特性と製造コストを解析し、両者の最適点が得られるようなコンデンサの組み合わせ条件を見つけ出す仕組みだ。

図3 初期設計を基にコンデンサ配置を最適化 OptimizePIによる最適化フローである。ユーザーによるボードの初期設計を基に、デカップリング・コンデンサの品種や搭載位置を変更しながらインピーダンス特性と製造コストを解析し、両者の最適点が得られるようなコンデンサの組み合わせ条件を見つけ出す仕組みだ。ユーザーはまず、ボードの設計データとして、電源分配回路の初期設計(具体的にはデカップリング・コンデンサの配置作業)を終えたレイアウト情報を、プリント配線基板用CADツールから読み込む*5)。つまりこのツールは、最適な電源分配回路をまったくのゼロから自動的に生成するのではなく、ユーザーの初期設計を出発点として、最適化を進める。

こうした手法を採用した理由は、電源分配回路は通常、前述の通り過剰に設計されているからだ。つまり、必要以上に数多くのデカップリング・コンデンサが搭載されている。品質を低下させないように注意しながら不要なコンデンサを取り去ることで、電源分配回路の最適化を実現できる。具体的には、初期設計で定められた各搭載位置に実際にコンデンサを搭載するか、搭載しないか、搭載する場合はどの品種を選択すればよいかを最適化すれば、電源品質を維持しながら製造コストを削減できるわけだ。

このほか、電源分配回路の初期設計はコンピュータ・ツールによる自動化が現実的でないという理由もある。例えば、デカップリング・コンデンサの実装に向けたパッドやビア・ホールは、信号トレースとの位置関係を考慮して配置しなければならない。この作業は複雑で、少なくとも現時点では、技術者による判断が不可欠だ。

電気特性/コストをモデル化

部品ライブラリは、あらかじめユーザーが作成しておく。ユーザーが所属する企業の推奨部品リストに登録されたデカップリング・コンデンサについて、特性情報を収めることを勧める。一般に推奨部品リストに登録されたデカップリング・コンデンサの品種は、100個以下と比較的少ない。また、1枚のボードに実際に搭載される品種は、15品種以下であることが多い。

各デカップリング・コンデンサの特性情報として収録するのは、部品種別やメーカー名、型名、RLC値、外形寸法のほか、電気特性モデル、製造コスト・モデルである。このうち電気特性モデルとして登録可能な情報には、簡単なRLC等価回路モデルのほか、SPICEネットリストやSパラメータの測定データがある。製造コスト・モデルは、部品コストと実装コストの情報で構成する。部品コストはデカップリング・コンデンサの単価である。実装コストは、プリント配線基板の製造に要するドリル、めっきなどの加工や材料の費用と、部品搭載に要するマウンタの償却費や人件費、間接材料費などをデカップリング・コンデンサ1個当たりに換算した金額である。

開発した最適化ツールには、この部品ライブラリを構築/管理する機能を用意した。部品ライブラリは、いったん作成してしまえば、その後開発するすべてのボードの設計に利用できる。

膨大な組み合わせを解析

部品ライブラリを作成し、レイアウト情報を読み込んだら、いよいよ最適化の工程に移る。

最初は、電源分配回路の電気的な特性を抽出する。これに向けてユーザーは、簡単なセットアップ情報を入力する必要がある。所要時間は30分程度だ。まず、初期設計において搭載されたデカップリング・コンデンサのうち、最適化の対象にするものを指定する。

続けて、ボードに搭載するDC-DCコンバータについて、等価直列抵抗とインダクタンスからなる等価回路モデルを記述するとともに、電源分配回路への接続個所を指定する。

さらに、ボード上のデジタルLSIについて、パッケージ内やチップ上の電源分配回路の等価回路モデルが手元にあれば入力する。ただし一般に半導体ベンダーは、こうした等価回路モデルを公開していない。従って、入手できない場合には、入力は不要だ。ボード上のデカップリング・コンデンサが機能する周波数範囲については、最適化に支障は生じない。

このほか最適化パラメータとして、ターゲット・インピーダンスや、利用を許容するデカップリング・コンデンサの外形寸法(すべてのサイズ/初期設計と同一サイズのみ/同一サイズ以下のみを許容)などを定義する。

セットアップ情報の入力が完了すると、ツールが電源分配回路の電気的な特性を解析する。

まず、すべてのデカップリング・コンデンサを搭載していない状態の電源分配回路の特性を、準3次元の有限要素法による電磁界解析や、伝送線路解析を使って抽出する。デカップリング・コンデンサを搭載していない状態だが、その搭載に向けたパッドやビア・ホールの寄生成分は考慮している。次に、デカップリング・コンデンサを各実装位置に搭載した状態の特性を、線形回路解析で求める仕組みだ。

この後は、デカップリング・コンデンサの実装位置それぞれに、部品ライブラリに収録されたさまざまな品種を順列組み合わせで次々と接続し、各状態における電源分配回路の特性を解析する。

この工程では、ユーザーが設定しておいた製造コストの許容範囲に収まるような、デカップリング・コンデンサの組み合わせ条件を数多く生成する。ツールの内部では数千もの組み合わせ条件について特性を解析しているのだが、ユーザーに対しては、あるコストで実現性の最も高い条件のみを示すようにした。

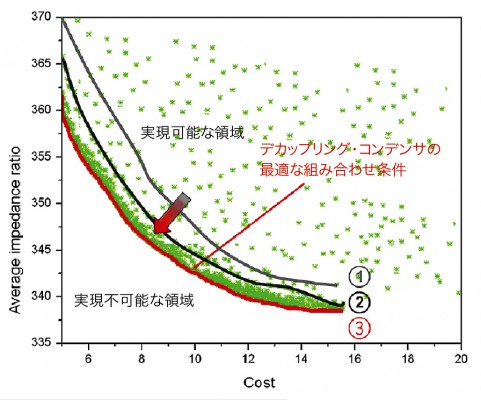

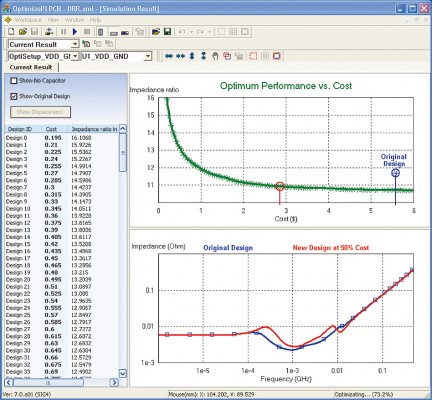

図4が解析結果の例である。コンデンサの品種と搭載位置のさまざまな組み合わせについて解析した結果をプロットしたものだ。緑色の点1つ1つが、解析した組み合わせ条件を示している。縦軸は電源分配回路全体のインピーダンス特性で、値が低いほど電源品質が高いことを表す。この例では、ツールによる処理の時間経過とともに解析結果は図4中の(1)のラインから(2)のラインに向かって進み、最終的には、(3)のラインにたどり着いた。ユーザーは、デカップリング・コンデンサの組み合わせとしてこの(3)上の条件を適用すれば、あるレベルの電源品質を最も低い製造コストで実現できるわけだ。

図4 コストと品質のトレードオフを可視化 最適化アルゴリズムによって得られた結果の例である。横軸は電源分配回路の製造コストだ。縦軸は電源分配回路全体のインピーダンス特性で、低い方が電源品質が高いことを表す。緑の点1つ1つは、デカップリング・コンデンサのある組み合わせ条件を示している。緑の点のほとんどが最終的な結果である(3)ラインの近くに位置していることから、最適化アルゴリズムの効率が高いことが分かるだろう。

図4 コストと品質のトレードオフを可視化 最適化アルゴリズムによって得られた結果の例である。横軸は電源分配回路の製造コストだ。縦軸は電源分配回路全体のインピーダンス特性で、低い方が電源品質が高いことを表す。緑の点1つ1つは、デカップリング・コンデンサのある組み合わせ条件を示している。緑の点のほとんどが最終的な結果である(3)ラインの近くに位置していることから、最適化アルゴリズムの効率が高いことが分かるだろう。良否判断の指標を導入

このツールにおいて最適化を担うのは単なるコンピュータ・アルゴリズムにすぎない。従って、デカップリング・コンデンサの最適な組み合わせ条件を見つけ出す際には、ある組み合わせ条件での電源品質が、別の組み合わせ条件のそれに比べて「良い」か「悪い」かの2値判断を下す必要がある。

開発したアルゴリズムでは、平均インピーダンス率(Average Impedance Ratio)と呼ぶ独自の評価指標を導入し、これを比較することで組み合わせ条件の優劣を判断した。この指標は、電源分配回路のインピーダンスについて、周波数帯域にわたる平均値と、ボード上のLSIそれぞれから見た平均値の2つをパラメータとするスカラー値である。これには非常に多くの情報が凝縮されており、電源品質の良否を判断する指標として十分に機能する。

最適化結果をユーザーが評価しやすくするために、図5に示す通り、ボード全体の電源分配回路のインピーダンス特性(前述の平均インピーダンス率)と、特定のLSIから見た電源分配回路のインピーダンスの両方を後処理によって表示する機能を用意した。

図5 ユーザー評価向け情報を後処理で表示 最適化によって得られたデータを後処理し、ユーザーが評価しやすくするための情報を提供する機能を用意した。画面右上はボード全体の電源分配回路のインピーダンス特性とコストの相関図。右下は、ボード上の特定のLSIから見た電源分配回路のインピーダンス特性である。

図5 ユーザー評価向け情報を後処理で表示 最適化によって得られたデータを後処理し、ユーザーが評価しやすくするための情報を提供する機能を用意した。画面右上はボード全体の電源分配回路のインピーダンス特性とコストの相関図。右下は、ボード上の特定のLSIから見た電源分配回路のインピーダンス特性である。製造コストと電源品質のトレードオフを評価する際には、通常はボード全体のインピーダンス特性に注目すればよい。例えば図5では、製造コストが2〜3米ドルを超えると、それ以上にコストを掛けてもインピーダンス特性があまり向上しなくなることが読み取れる。つまり品質に寄与しない無駄なコストを見極められる。また、LSIごとのインピーダンス特性を検証すれば、電源品質の改善を妨げているLSIを素早く見つけ出せる。

インタラクティブな「What−If解析」機能も用意した。最適化の結果として得られたデカップリング・コンデンサの組み合わせ条件に対して、さまざまなパラメータを変更しながら、その変更の影響を評価できる。例えば最適化によって、ある1品種のデカップリング・コンデンサのみを適用した組み合わせ条件が得られたとしよう。ここでWhat−If解析機能を使えば、このコンデンサを別の品種に変更して製造コストを低減できるかどうかを素早く検証できる。

こうして得られたデカップリング・コンデンサの最適な組み合わせ条件は、最終的には、デカップリング・コンデンサの搭載位置情報をまとめた表形式のファイルとして出力される。この表には、初期設計で指定した各コンデンサの搭載位置に対する、最適化後のコンデンサ搭載/非搭載の情報と、搭載する場合の品種が示してある。

ここまでに説明した最適化手法は、電源分配回路に向けた現行の設計フローを変更するのではなく、拡張するものだということに注目してほしい。このためユーザーは、新たな作業を増やすことなく、電源品質を高めたり、製造コストを低減したりできる。

このほか、初期設計で配置したデカップリング・コンデンサの多くを実際には搭載しないようにすれば、製造コストの低減のみならず、非搭載位置のビア・ホールやパッドを取り除くことで、ボード上の有効面積を増やすことも可能だ。有効面積が増えれば配線が容易になったり、層数やボード・サイズを削減できる可能性もある。

非搭載位置のビア・ホールやパッドはユーザーが手作業で取り除く必要があるものの、これによって電源品質が悪化する危険性は低い。電気的には、寄生インダクタンスや寄生キャパシタンスが削除されることに等しいからだ。もちろん、スイッチング電流のリターン経路の一部が変化し、電源分配回路全体の特性に微小な差異を生じる可能性は皆無ではない。この場合も、レイアウト変更後の設計データを読み込んで再度解析すれば、電源品質に与える影響を簡単に確認できる。

コスト低減効果を確認

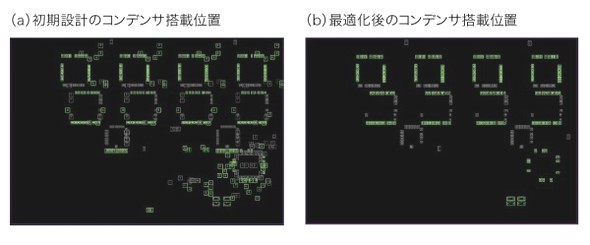

最後に、この最適化ツールを実際に採用したユーザーの事例を2つ紹介しよう。1つ目は、8個のFPGAと3つのデジタルLSIを搭載した大型ボードである。図6(a)は初期設計におけるデカップリング・コンデンサの搭載位置、図6(b)は最適化後の搭載位置を示す。この電源分配回路の製造コストは、初期設計では24.65米ドルだったが、最終的には14.04米ドルに低減できた。43%のコスト削減である。電源品質については、初期設計と同等のインピーダンス特性を確保するように最適化した。

図6 コンデンサの使用個数を削減 (a)は、初期設計におけるデカップリング・コンデンサの搭載位置。(b)は、最適化後の搭載位置である。緑色のシンボルは表層に搭載したコンデンサで、灰色のシンボルは裏面に搭載したコンデンサを表す。この例では、ボード全体のインピーダンス特性が初期設計と同じになるように最適化した。つまり、同じ電源品質でコンデンサの数を減らせたことになる。

図6 コンデンサの使用個数を削減 (a)は、初期設計におけるデカップリング・コンデンサの搭載位置。(b)は、最適化後の搭載位置である。緑色のシンボルは表層に搭載したコンデンサで、灰色のシンボルは裏面に搭載したコンデンサを表す。この例では、ボード全体のインピーダンス特性が初期設計と同じになるように最適化した。つまり、同じ電源品質でコンデンサの数を減らせたことになる。2つ目の事例は、DDR3に対応したメモリー・モジュールである。36個のDRAMチップを搭載したDIMM(Dual Inline Memory Module)ボードである。やはり初期設計と同等のインピーダンス性能を確保するように最適化し、電源分配回路の製造コストを32%削減できた。

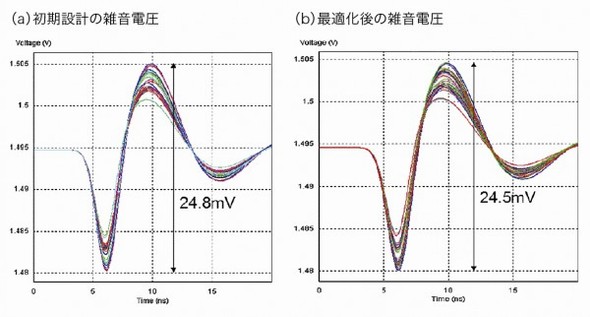

図7は、36個のDRAMチップそれぞれの電源端子において、雑音電圧の挙動を時間領域で解析した結果である。各DRAMチップの電源端子とグラウンド端子の間に同じタイミングで、振幅が50mAで幅が4nsのガウス波形の電流パルスを雑音源として与えて解析した。

この結果からは、周波数領域の特性である電源分配回路全体のインピーダンス特性を確保することで、時間領域の特性である雑音電圧を低く抑えられることが読み取れる。ここから、電源分配回路の最適化に向けて、周波数領域の特性であるターゲット・インピーダンスを指標に使う妥当性を確認できた。

図7 時間領域の特性も最適化できる DDR3対応メモリー・モジュールに搭載した36個のDRAMチップそれぞれにおける雑音電圧の時間変化を解析した。(a)が初期設計、(b)が最適化後の結果である。周波数領域におけるボード全体のインピーダンス特性を初期設計と同程度に維持するよう最適化した。この波形から、時間領域での特性も維持されていることが確認できる。

図7 時間領域の特性も最適化できる DDR3対応メモリー・モジュールに搭載した36個のDRAMチップそれぞれにおける雑音電圧の時間変化を解析した。(a)が初期設計、(b)が最適化後の結果である。周波数領域におけるボード全体のインピーダンス特性を初期設計と同程度に維持するよう最適化した。この波形から、時間領域での特性も維持されていることが確認できる。【注釈】

*3)価格はノード・ロック方式で永久ライセンスが929万5000円、1年間限定ライセンスが403万6500円である。連絡先は国内における販売とサポートを手掛けるATEサービス デザイン・ソリューション・グループ、電話044-850-8715。

*4)電源分配回路の動的な振る舞いである周波数特性を解析するシミュレータや、静的な振る舞いである直流電圧降下(IRドロップ)や電流の集中個所を検証するシミュレータである。例えば米Sigrity社は動的解析向けの「PowerSI」と静的解析向けの「PowerDC」を提供中だ。

*5)ボードのレイアウト情報は、主要なCADツールからインポートできる。具体的には、オーストラリアのAltium社や米Cadence Design Systems社、米Mentor Graphics社、ワイ・ディ・シー、図研などが提供するプリント配線基板用CADツールである。読み込む情報は、レイアウト・パターンや層構成(スタックアップ)、ネット名称などである。

Profile

Brad Brim氏は現在、米Sigrity社でICパッケージやプリント配線基板の特性抽出に向けたEDAツールのプロダクト・マーケティング・マネジャーを務めている。電磁界解析ツールや高周波回路設計ツールの分野で約20年の経験を有する。本田 裕(ほんだ ゆたか)氏は現在、ATEサービスでシニア・アプリケーション・エンジニアを務めている。なお同社は、Sigrity社のEDAツールの国内における販売やサポートを担う代理店である。このほかシグナル・インテグリティ関連のEDAツールの販売/技術サポートや、半導体テスト分野の機器販売やコンサルティングなども手掛けている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- 全固体電池の製造プロセス簡素化、東北大が新手法

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- ソニー、新会社「BRAVIA」にテレビ事業を承継 企業価値1028億円