CMOSが拓く次の応用 〜 ISSCC 2009開催:アナログ設計(2/5 ページ)

第1部 ミリ波無線のCMOS化が加速、フル機能の1チップ集積が視野に

60GHz帯や77GHz帯といったミリ波帯を民生用途で活用すべく、CMOS技術による無線チップの開発が活発だ。デジタル家電機器の間で高品位のビデオ信号を非圧縮のまま無線伝送するインターフェースや、自動車の安全機能に向けたレーダー装置などを視野に、ミリ波帯の利用コストを大幅に下げることを目指す。

これまでミリ波帯の無線回路は、動作周波数を高くでき、高周波特性に優れたGaAs(ガリウム・ヒ素)などの化合物半導体を使って構成することが一般的だった。化合物半導体は、チップ自体の製造コストが高い上、集積度を高めにくく、無線回路を構成するチップの枚数が多くなるため、組み立てコストも高かった。ところが最近になって、トランジスタの動作周波数が微細化によって高まったことに加え、素子のモデリング技術の進展や回路アーキテクチャの工夫などによって、CMOS技術でミリ波帯の無線回路を実現できるようになってきた。それも、SiGe(シリコン・ゲルマニウム)材料などの化合物材料を使ったり、SOI(Silicon on Insulator)構造を採ったり、BiCMOS(バイポーラCMOS)プロセスを導入したりすることなく、バルクSi(シリコン)ウエハーを用いた論理LSI向けの標準的なCMOS技術である。

すでに無線回路の構成要素(ビルディング・ブロック)については数多くの開発成果があり、実用化も進んでいる。現在は無線信号の送受信機能を1枚のチップに集積したり、さらにベースバンド処理機能を含めた1チップ化への取り組みが進行中である。

77GHz車載レーダーの送受信部を集積

富士通研究所は、90nmの標準CMOS技術を適用した77GHz帯の車載ミリ波レーダー向け無線送受信ICを発表した(講演番号は18.3)。送信部のパワー・アンプとその前段のゲイン・アンプや、受信部の低雑音アンプ(LNA)とその後段のゲイン・アンプ、IF変換用ミキサーのほか、38GHzの発振器の出力を2てい倍して77GHzの基準信号を生成する回路と、その基準信号を送信部と受信部に分配する回路を1チップに集積した。

「77GHz帯の無線送受信ICをCMOS技術で実現したのは世界初だ。CMOS技術の成果としてこれまでに学会報告されていたのは、77GHz帯では増幅器ICなどの要素回路にとどまっており、60GHz帯でも送信ICや受信ICが数件、送信と受信の両機能を集積したICは1件だけだった」(同社)。今後、CMOS技術で無線送受信部とベースバンド処理部を1チップに集積できれば、車載レーダーの小型化や低価格化を実現できると期待されており、今回の成果はそれに近づく一歩だといえる。

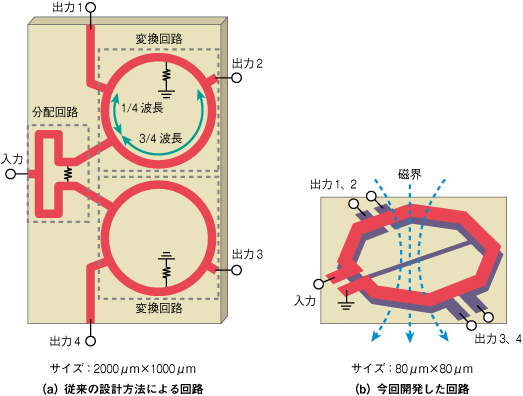

同社によれば今回、CMOS技術で77GHz帯の無線送受信ICを実現する際に大きく2つの課題を解決したという。第1の課題は、77GHzの基準信号を送信部と受信部に分配する回路の面積が大きくなってしまうことである。同社が試算したところ、伝送線路素子を利用した分布定数回路で構成する場合に2mm×1mmに達した。CMOS技術を採用するためには、基準信号生成回路の出力を2つに分岐する分配器に加えて、基準信号生成回路が出力するシングルエンド信号を差動信号に変換する回路も必要になるからだ。「CMOS技術は、論理回路も1チップに集積できるというメリットがある半面、電源系の雑音が大きくなってしまう。そのため無線送受信部は、耐雑音性を高めるため差動化が不可欠だ」(同社)。

そこで同社は今回、差動変換に分布定数回路ではなく、差動トランスを採用した(図1)。すなわち、多層配線を利用して1個の1次側コイルと2個の2次側コイルを作り込み、1次側をシングルエンド信号で駆動することで、2次側から2系統の差動信号を取り出した。このコイルの専有面積は80μm×80μmと小さい。差動トランスを差動化に使う手法自体は従来からあったが、今回は2次側コイルの構造を工夫することで損失を低く抑えたという。具体的には、複数層を使うスパイラル型とせず、単層に半円型に形成した。「トランスとしての結合係数は約0.6と比較的低くなってしまったが、伝送線路による損失は低減できた」(同社)。

図1 差動化/分岐回路を差動トランスで省面積化 77GHzの基準信号を差動化して送信部と受信部に2分配する回路である。(a)に示すような、伝送線路による分布定数回路を利用した従来型の方式では、チップ上の専有面積が大きくなってしまう。そこで今回は(b)に示すように、差動トランスを使って差動化する手法を採用した。出典:富士通研究所

図1 差動化/分岐回路を差動トランスで省面積化 77GHzの基準信号を差動化して送信部と受信部に2分配する回路である。(a)に示すような、伝送線路による分布定数回路を利用した従来型の方式では、チップ上の専有面積が大きくなってしまう。そこで今回は(b)に示すように、差動トランスを使って差動化する手法を採用した。出典:富士通研究所インピーダンス整合回路も省面積化

第2の課題は、77GHzの信号を伝送する際にトランジスタ素子間のインピーダンス整合回路の面積が大きくなってしまうことである。一般にこの整合回路は、伝送線路を素子として利用した分布定数回路で構成する。インピーダンスの移相量を細かく調整しやすいからだ。ただし分布定数回路は、インダクタなどのいわゆる集中定数素子を利用する手法に比べると、専有面積が大きくなってしまう。

そこで同社は今回、必要な移相量は小さいが、高い精度で移相量を設定しなければならない部分と、必要な移相量は大きいが、移相量の設定精度は問題にならない部分に切り分けて、前者に対しては従来通り分布定数回路を適用し、後者については集中定数素子を利用した。具体的には、トランジスタ素子に電源(バイアス)を供給する経路は大きな移相量が必要だがその設定精度については低くて構わないため、集中定数素子であるスパイラル・インダクタを適用した。一方で、77GHzの信号が直接通過する経路については、伝送線路による分布定数回路を適用した。

こうした工夫の結果、チップ全体の面積を1.2mm×2.4mmに抑えられた。「これまで学会などで報告されている、30G〜300GHzのミリ波帯に対応した無線送信ICや無線受信ICの中でも、世界最小サイズだ」(同社)と主張する。このほかの主な特性は以下の通りである。チップ全体の消費電力は920mW。送信部は出力周波数が73.5G〜77.1GHz、出力電力が3.3〜6.3dBm。受信部は変換利得が50Ω負荷において2.0±1.5dB、LNAの雑音指数が77GHzにおいて6.8dB、消費電力が260mW。基準信号発生部は同調範囲が73.5G〜77.1GHz、位相雑音特性が1MHzオフセットにおいて−83dBc/Hz、消費電力が270mWである。

45nmで60GHz無線の構成要素を実現

独立研究機関であるベルギーIMECは、45nmの標準CMOS技術を適用した60GHz帯の無線送受信向けIC群について発表した(図2)。RF受信フロントエンドICとPLL(Phase Locked Loop)IC、送信用パワー・アンプICの3つである。IMECによれば、これらの構成要素を基に、2010年までには60GHz帯の無線送受信回路全体をデジタルCMOS技術で1枚のチップに集積できるようになり、ミリ波帯利用の無線通信技術が第2世代に突入するという。

RF受信フロントエンドICには、LNAと周波数変換用ミキサーを集積した(講演番号は29.5)。57G〜66GHzに対応する。雑音指数(NF)は6dBと低い。さらに回路面積は150μm×150μmと小さく、消費電流は電源電圧が1.1Vのときに19mAと低い。外部からデジタル信号で制御できることを特徴としており、バイアス電圧の調整によるアナログ的な制御は不要だ。従って、「フェーズド・アレイ方式の受信システムに理想的である」(IMEC)。PLL ICは、同調範囲が広いことを特徴としており、具体的には57G〜66GHzをカバーする(講演番号は29.6)。直交位相信号を出力するため、ゼロIF方式の受信回路に使える。消費電力は電源電圧が1.1Vのときに78mWと小さい。送信用パワー・アンプICは、50G〜67GHzに対応した(講演番号は22.5)。プッシュプル方式を採用しており、1dB圧縮ポイント(P1dB)は電源電圧が1.1Vのときに11dBmである。

これらの成果からIMECは、「受信機を構成した場合、16個のアンテナ・パスを利用することで、非圧縮の高品位(HD)ビデオをわずか1.6Wの消費電力で10mにわたって無線伝送できる」としている。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- 「世界初」成果で1000層超3Dフラッシュに道筋、キオクシアとSandisk

- ソニー半導体、26年度は減収見込み メモリ市況不透明

- ナフサ危機で迫る「レジスト供給途絶」――世界の半導体工場を停止させる、もう一つの臨界点

- ペロブスカイト/CIGSタンデム太陽電池で「世界最高」効率達成、東京都市大ら

- 「画素の製造もパートナーと」十時氏が語る、ソニー×TSMC合弁の狙いと期待

- TSMCが次世代ロードマップ公表 A13/A12を29年投入へ

- DRAM不足で変わるAIシステム設計 エッジAIや特化型モデルに追い風

- ソニーセミコンとTSMCが合弁会社設立を検討

- 半導体検査装置向けレンズの研磨工程が稼働、生産能力2.6倍に

- 26年3月の世界半導体市場は79%増、日本も10カ月ぶりプラス成長

図2 45nmのCMOS技術で製造した60GHz帯IC LNAやミキサーを集積したRF受信フロントエンドICである。雑音指数は6dBに抑えた。出典:ベルギーIMEC

図2 45nmのCMOS技術で製造した60GHz帯IC LNAやミキサーを集積したRF受信フロントエンドICである。雑音指数は6dBに抑えた。出典:ベルギーIMEC