炭素はどこまでシリコンに取って代われるか、3種類の材料が商用化に向かう:材料技術(4/5 ページ)

グラフェンが抱える2つの課題

電子機器向けのカーボン技術の中で、商用化までの道のりが最も遠いと言われているのがグラフェンだ。しかし、グラフェンは、Si半導体プロセスとの統合という点では、最も可能性を秘めた素材といえる。2次元構造を持つグラフェンを用いたトランジスタは、単純に考えて、3次元構造を持つダイヤモンドや、1次元構造を持つカーボンナノチューブよりも、現在、主流を占めている2次元半導体製造プロセスに適合しているからだ。

グラフェンを半導体の主力技術として採用するには、解決しなければならない問題が2つある。1つ目がバンドギャップだ。グラフェンはバンドギャップを持たないため、デジタル素子への採用は難しい。だが、アナログトランジスタには使える。DARPAが実施するRF用途に向けたカーボンエレクトロニクスを研究するCERA(Carbon Electronics for RF Applications)プログラムは、アナログトランジスタを開発対象としている。CERAでは、2012年までに、グラフェントランジスタを用いた94GHzのパワーアンプのデモを披露したい考えだ。

CERAの研究を先導するIBMのAvouris氏は、「当社の研究所では、50GHzでグラフェントランジスタの動作を確認済みだ。次は、数百GHzとさらに高い周波数を狙う」と話す(図3)。

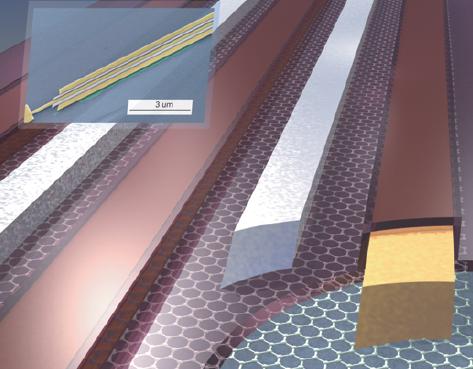

図3 米IBMのアナログトランジスタの構造 米IBMは、DARPAが実施するCERAプログラムの成果として、グラフェンチャネル(6角形の格子構造で描いた)を用いた50GHzで動作するアナログトランジスタを開発した。同社は2012年までに、グラフェントランジスタを利用したテラヘルツ(THz)級パワーアンプの開発を狙う。

図3 米IBMのアナログトランジスタの構造 米IBMは、DARPAが実施するCERAプログラムの成果として、グラフェンチャネル(6角形の格子構造で描いた)を用いた50GHzで動作するアナログトランジスタを開発した。同社は2012年までに、グラフェントランジスタを利用したテラヘルツ(THz)級パワーアンプの開発を狙う。他の研究所も、グラフェンを利用する高周波トランジスタの研究開発を急ピッチで進めている。米Georgia Institute of Technologyの教授であるWalter de Heer氏は、「当研究所では、グラフェンをベースにした超高周波トランジスタを1年以内に完成させる予定だ。同トランジスタの製造に伴う基本的な問題はほぼ解決した。残された問題は、グラフェンに適合する誘電材料を見つけることと、誘電材料を確実に成膜する方法を探ることだ。この2つは、材料を問わず新たな半導体プロセスの開発には避けて通れない問題である」と述べた。

一方、ワイドバンドギャップ半導体の専門家である米Massachusetts Institute of Technology(MIT)のTomas Palacios氏は多くのライバルに先駆けて、バンドギャップを必要としない周波数増幅器に向けたアナログ回路を、グラフェンを用いて製造した。「われわれが探していたのは、グラフェンを使用したまったく新しい素子、つまり、従来の技術では到達不可能な性能を発揮する素子だ」とPalacios氏は明かす。

大面積のグラフェンを作れない

グラフェンが直面するバンドギャップの問題に次ぐ課題は、スケーリングだ。スケーリング問題が解決されない限り、グラフェンが主要製造技術に取り込まれることはない。CVD(Chemical Vapor Deposition)技術の適用範囲は約25mm(1インチ)のウエハーに制限されているため、研究者はMBE(Molecular Beam Epitaxy)法とSiC熱処理法に頼らざるを得ない。SiC熱処理法ではSiCウエハーを1100℃まで加熱してSiを昇華させることで、グラフェンで被覆されたウエハーを形成する。

Palacios氏の研究チームでは、同氏の同僚でMITの教授であるJing Kong氏が開発したCVD手法を用いている。これは、Ni(ニッケル)で被覆したSiウエハー上に、センチメートル(cm)サイズのグラフェン膜を成長させる手法だ。MITの研究チームはエッチング処理でNiを除去し、成長したグラフェン膜を元のSiウエハーからほかの基板上へと移すことに成功した。

Palacios氏は、「この技術によって、さまざまな種類の基板をテストできるようになった。SiCや、ダイヤモンド、GaN基板から、柔らかいプラスチック基板に至るまで、あらゆる基板にグラフェン回路を実装できる」と主張する。

MITは、グラフェンを商用チップの材料として利用できるようにするという目標を掲げ、5年にわたる研究を開始した。5年にわたるMURI(Multidisciplinary University Research Initiative)プログラムは、米空軍と米海軍を加えて共同で進めるという。空軍はこのプログラムを通じて、高品質かつ均一で、欠陥のないエピタキシャル成長条件を探り、同材料の物性を研究し、化学センサーや圧力センサー、生物学的センサーといった潜在的な用途の特定を狙う。一方、ONR(Office of Naval Research、米海軍海事技術本部)はMURIプログラムを通じて、グラフェンの電気的な特性を明らかにし、10nm未満のナノ構造グラフェンを使用して、画期的な装置に向けた機能や回路の開発を目指す。

Copyright © ITmedia, Inc. All Rights Reserved.

記事ランキング

- オムロン、祖業の電子部品事業を売却へ 事業価値810億円

- パワー半導体再編が本格化 ローム・東芝・三菱電機が協議開始へ

- もはや半導体メーカーの域を超えた NVIDIA最新エッジ機器を分解

- 魚津はTower、砺波はNuvotonに TPSCo事業の再編を発表

- 「究極の半導体」ダイヤモンドを社会へ 動態展示も実現の早大発新興

- 「Renesas 365」がついに始動 「不可能だった規模」の検証、数分で

- 全固体電池の製造プロセス簡素化、東北大が新手法

- Wi-Fi HaLow日本市場がついに加速か 850MHz帯解放も後押し

- JDIが鳥取工場を売却、車載用液晶パネル拠点

- NVIDIAとメモリ3社、世界半導体売上高の42%占める